RET educativa descartes

# iCartesiLibri

# Electrónica Digital Ejemplos y Ejercicios

#### Oscar Ignacio Botero Henao

Fondo Editorial RED Descartes

Córdoba (España) 2025 Título de la obra: Electrónica Digital Ejemplos y Ejercicios

Autor:

Oscar Ignacio Botero Henao

Código JavaScript para el libro: <u>Joel Espinosa Longi, IMATE</u>, UNAM.

Recursos interactivos: <u>DescartesJS</u>, <u>WebSim</u>

Fuentes: Lato y UbuntuMono

Figura de portada: ilustración generada por Nightcafe Al

Red Educativa Digital Descartes Córdoba (España)

descartes@proyectodescartes.org

https://proyectodescartes.org

Proyecto iCartesiLibri

https://proyectodescartes.org/iCartesiLibri/index.htm

ISBN: 978-84-10368-22-4

# Tabla de contenido

| Pr | efacio                                   | 9  |

|----|------------------------------------------|----|

| 1. | Conversiones: Sistemas Numéricos         | 13 |

|    | 1.1 Conversión de Decimal a Binario      | 15 |

|    | 1.2 Conversión de Binario a Decimal      | 17 |

|    | 1.3 Conversión de Decimal a Octal        | 18 |

|    | 1.4 Conversión de Octal a Decimal        | 19 |

|    | 1.5 Conversión de Decimal a Hexadecimal  | 20 |

|    | 1.6 Conversión de Hexadecimal a Decimal  | 22 |

|    | 1.7 Conversión de Binario a Octal        | 23 |

|    | 1.8 Conversión de Octal a Binario        | 24 |

|    | 1.9 Conversión de Binario a Hexadecimal  | 24 |

|    | 1.10 Conversión de Hexadecimal a Binario | 25 |

|    | 1.11 Conversión de Octal a Hexadecimal   | 26 |

|    | 1.12 Conversión de Hexadecimal a Octal   | 28 |

|    | 1.13 Ejercicios propuestos con respuesta | 29 |

|    | 1.13.1 Decimal a Binario                 | 29 |

|    | 1.13.2 Binario a Decimal                 | 29 |

|    | 1.13.3 Decimal a Octal                   | 30 |

|    | 1.13.4 Octal a Decimal                   | 30 |

|    | 1.13.5 Decimal a Hexadecimal             | 30 |

|    | 1.13.6 Hexadecimal a Decimal             | 31 |

|    | 1.13.7 Binario a Octal                   | 31 |

|    | 1.13.8 Octal a Binario                   | 31 |

|    | 1.13.9 Binario a Hexadecimal             | 32 |

| 1.13.10 Hexadecimal a Binario               | 32  |

|---------------------------------------------|-----|

| 1.13.11 Octal a Hexadecimal                 | 33  |

| 1.13.12 Hexadecimal a Octal                 | 33  |

| Ayudas y Complementos                       | 37  |

| 1.14 Videos                                 | 39  |

| 1.15 Objetos Interactivos                   | 43  |

| 2. Álgebra de Boole                         | 51  |

| 2.1 Demostración de las Reglas de Absorción | 54  |

| 2.2 Ejemplos                                | 56  |

| 2.3 Ejercicios propuestos con respuestas    | 62  |

| Ayudas y Complementos                       | 65  |

| 2.4 Videos                                  | 67  |

| 2.5 Objetos Interactivos                    | 68  |

| 3. Operaciones Lógicas Binarias             | 71  |

| 3.1 Suma lógica Binaria                     | 73  |

| 3.2 Resta lógica Binaria                    | 79  |

| 3.2.1 Otro método de solución               | 88  |

| 3.3 Multiplicación lógica Binaria           | 93  |

| 3.4 División lógica Binaria                 | 98  |

| 3.5 Ejercicios propuestos con respuesta     | 106 |

| 3.6 Circuitos Sumadores                     | 108 |

| 3.6.1 Semi-Sumador (SS)                     | 108 |

| 3.6.2 Sumador Completo (SC)                 | 109 |

| 3.6.3 Ejemplos                              | 110 |

| 3.7 Circuitos Restadores                    | 116 |

| 3      | 3.7.1 Semi-Restador (SR)                                 | 116 |

|--------|----------------------------------------------------------|-----|

| 3      | 3.7.2 Restador Completo (RC)                             | 117 |

| 3      | 3.7.3 Ejemplos                                           | 118 |

| 3.8    | Multiplicador                                            | 129 |

| 3      | 8.8.1 Ejemplos                                           | 130 |

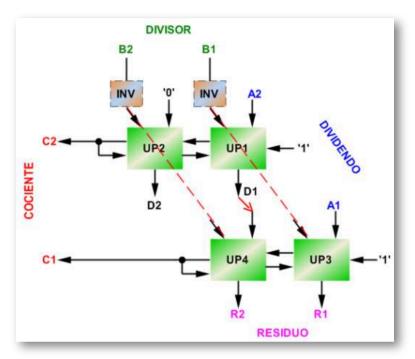

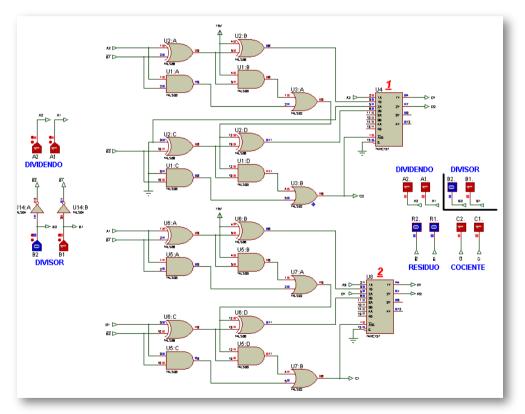

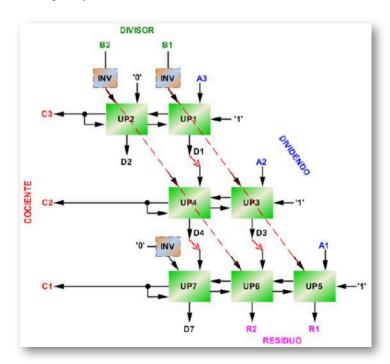

| 3.9    | Divisor                                                  | 133 |

| 3      | 3.9.1 Ejemplos                                           | 135 |

| 3.10   | O Ejercicios propuestos con respuestas                   | 140 |

| Ayuda  | as y Complementos                                        | 149 |

| 3.1    | 1 Videos                                                 | 151 |

| 3.12   | 2 Objetos Interactivos                                   | 154 |

| 3.13   | 3 Simulaciones                                           | 155 |

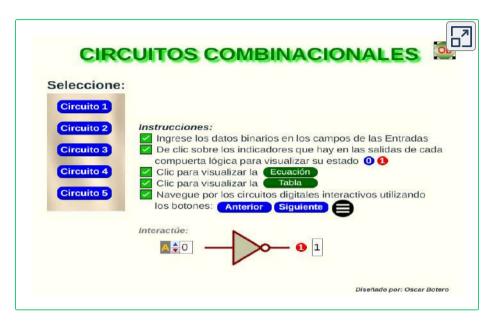

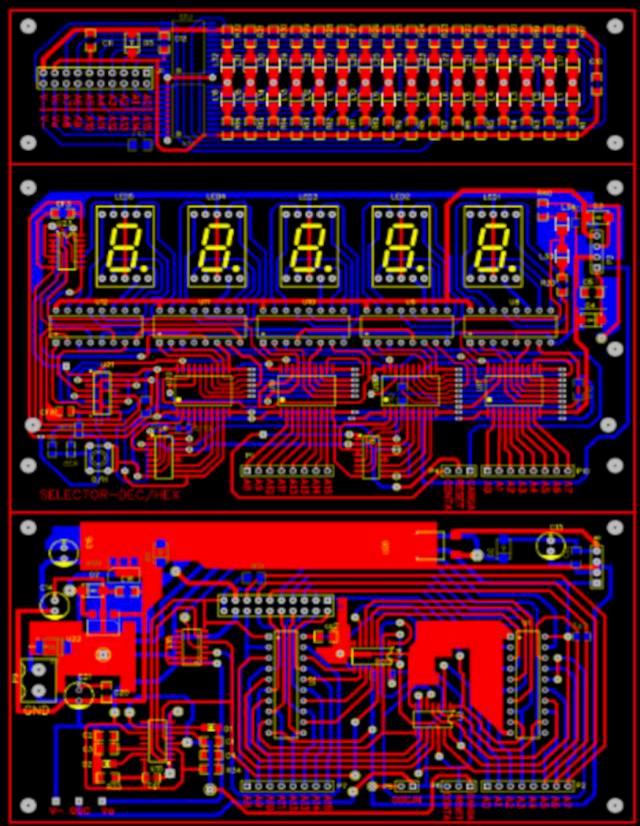

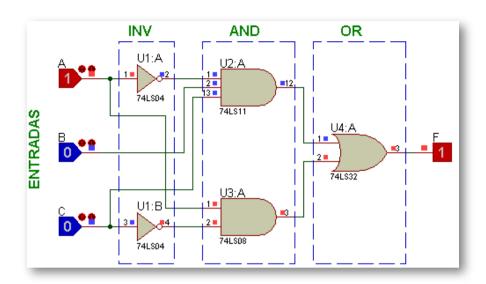

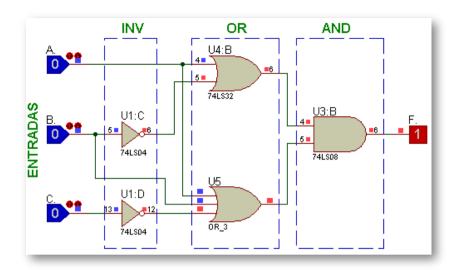

| 4. Fun | nciones Lógicas                                          | 157 |

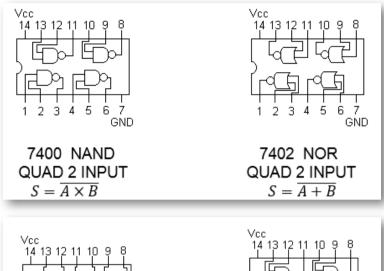

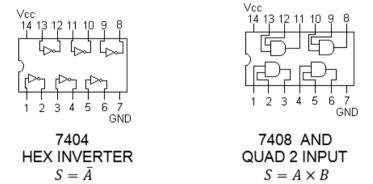

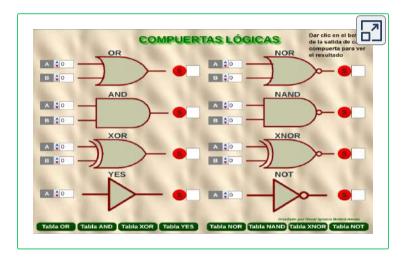

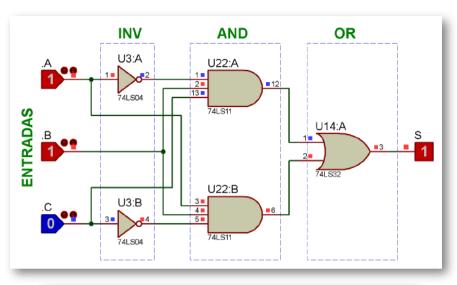

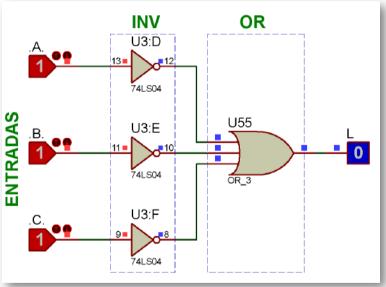

| 4.1    | Compuertas Lógicas                                       | 159 |

| 4.2    | Diagramas internos de las compuertas familia TTL         | 161 |

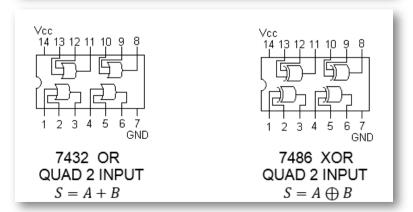

| 4.3    | Diagramas internos de las compuertas familia CMOS        | 162 |

| 4.4    | Referencias comerciales por familias y sus descripciones | 163 |

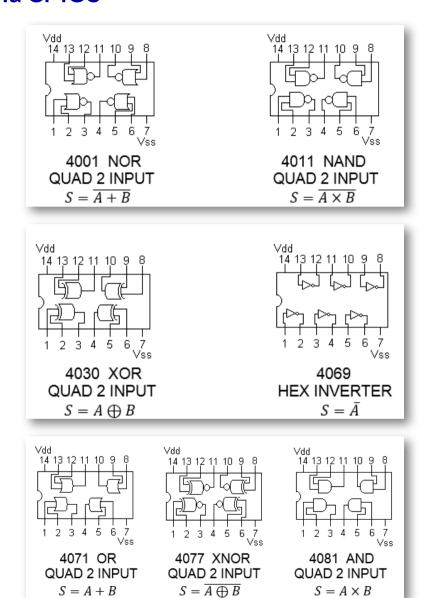

| 4.5    | Ejemplos basados en Funciones Lógicas                    | 163 |

| 4.6    | Ejemplos basados en el Circuito                          | 173 |

| 4.7    | Ejercicios propuestos con respuestas                     | 178 |

| 4      | .7.1 Basados en funciones lógicas                        | 178 |

| 4      | .7.2 Basados en el circuito                              | 180 |

| Ayuda  | as y Complementos                                        | 185 |

| 4.8    | Videos                                                   | 187 |

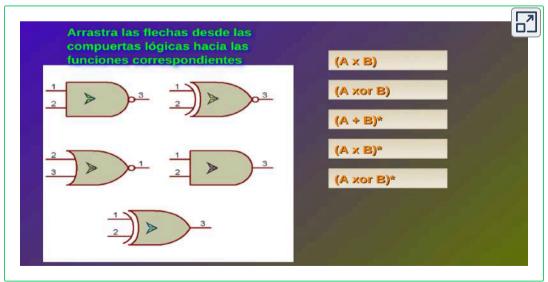

| 4.9    | Objetos Interactivos                                     | 190 |

| 4.10 Simuladores Circuitos Digitales               | 192 |

|----------------------------------------------------|-----|

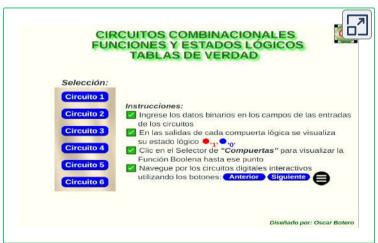

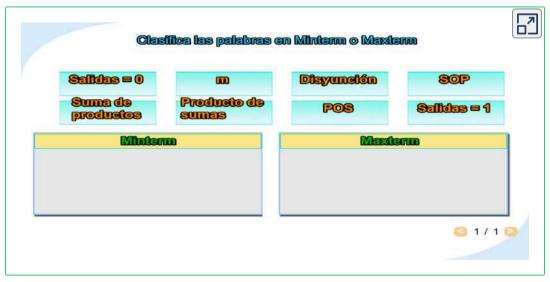

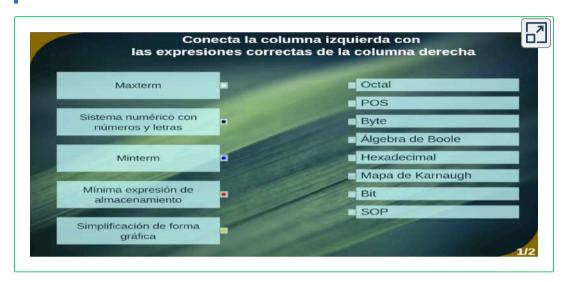

| 5. Minterm y Maxterm Lógica AOI                    | 195 |

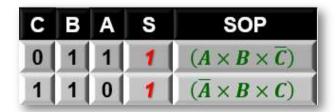

| 5.1 Ejemplos basados en la función lógica          | 197 |

| 5.2 Ejemplos basados en la tabla de verdad         | 201 |

| 5.3 Ejemplos basados en enunciados con condiciones | 204 |

| 5.4 Ejercicios propuestos con respuestas           | 212 |

| 5.4.1 Basados en funciones lógicas                 | 212 |

| 5.4.2 Basados en las tablas de verdad              | 213 |

| 5.4.3 Basados en enunciados con condiciones        | 215 |

| Ayudas y Complementos                              | 219 |

| 5.5 Videos                                         | 221 |

| 5.6 Objetos Interactivos                           | 222 |

| 5.7 Simulaciones                                   | 223 |

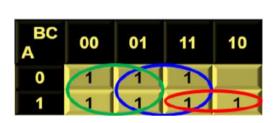

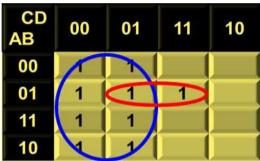

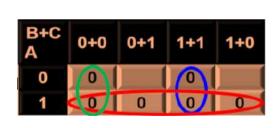

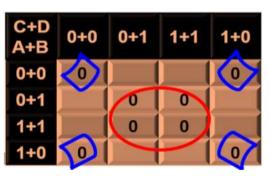

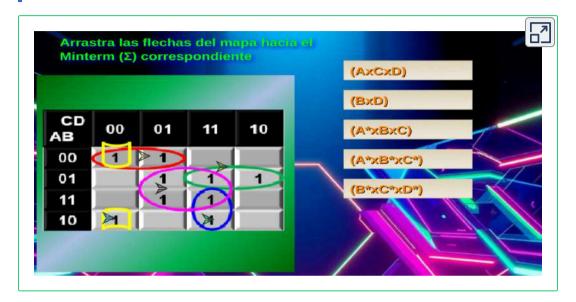

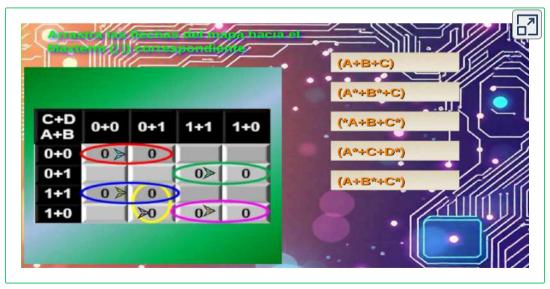

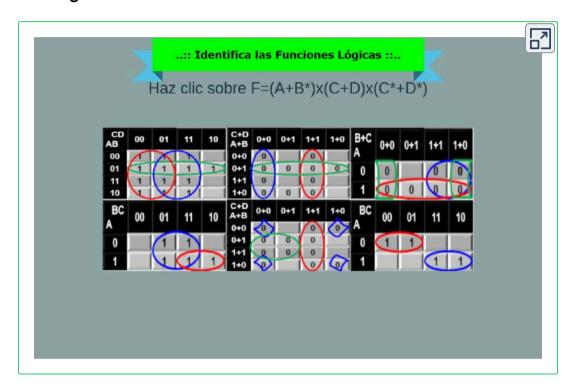

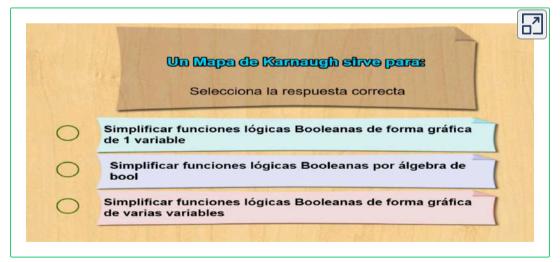

| 6. Mapas de Karnaugh                               | 225 |

| 6.1 Ejemplos basados en la tabla de verdad         | 229 |

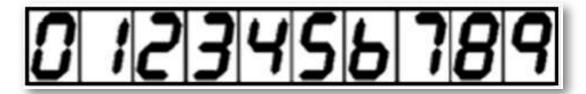

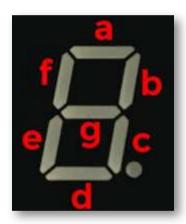

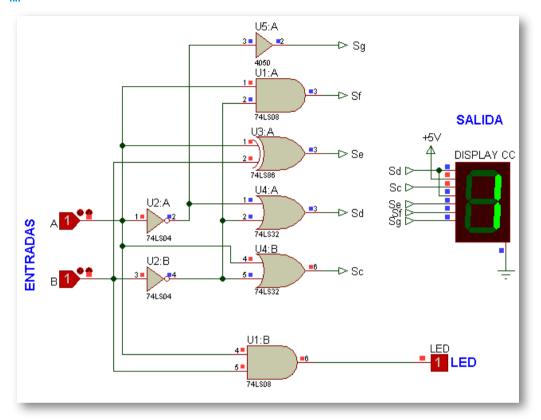

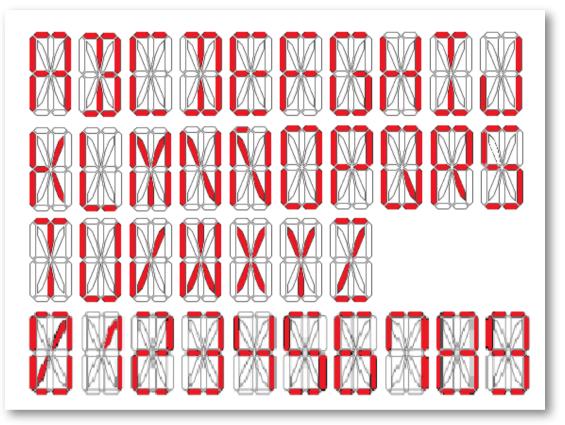

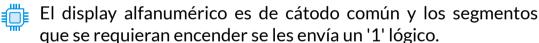

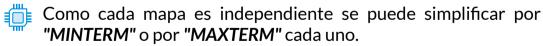

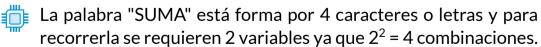

| 6.2 Ejemplo con secuencia de números y display     | 236 |

| 6.3 Ejemplo con un texto y display alfanumérico    | 240 |

| 6.4 Ejercicios propuestos con respuestas           | 245 |

| Ayudas y Complementos                              | 253 |

| 6.5 Videos                                         | 255 |

| 6.6 Objetos Interactivos                           | 256 |

| 6.7 Simuladores y Simulaciones                     | 258 |

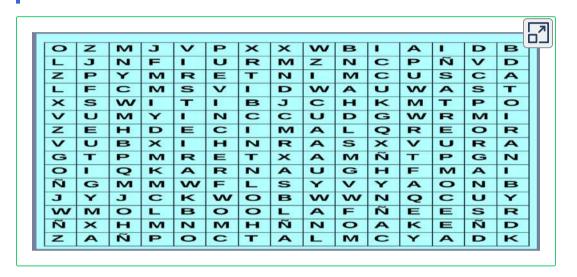

| Repaso                                             | 261 |

| Actividades de Repaso                              | 263 |

| Anexos 2                                | 267 |

|-----------------------------------------|-----|

| Anexo A Hojas de Datos                  | 269 |

| Anexo B Subfamilias de los CI TTL       |     |

| Anexo C Subfamilias de los CI CMOS      | 272 |

| Anexo D Sufijos de Fabricantes Actuales | 273 |

| Anexo E Principales Encapsulados CI     | 274 |

| Anexo F Símbolos estándar para CI       | 275 |

| Bibliografía                            | 277 |

### Prefacio

La electrónica digital es una disciplina fundamental en el campo de la ingeniería y la tecnología, abarcando desde los principios básicos de los sistemas numéricos hasta el diseño y la implementación de circuitos complejos con mediana escala de integración. Esta primera parte del libro "ELECTRÓNICA DIGITAL, Ejemplos y Ejercicios" ha sido concebido con el objetivo de proporcionar a estudiantes y profesionales una herramienta práctica y accesible para el estudio y la comprensión de los conceptos esenciales de la electrónica digital.

A diferencia de otros textos que se centran en la teoría y la explicación detallada de los principios y conceptos, esta obra se dedica exclusivamente a la resolución de Ejemplos y la proposición de Ejercicios con respuestas. Creo firmemente que la mejor manera de aprender y dominar los conceptos de la electrónica digital es a través de la práctica constante y la aplicación directa de los conocimientos adquiridos.

Los temas abordados que incluye este libro son:

# Capítulo 1: Conversiones Sistemas Numéricos:

o Este tema abarca la transformación de números entre distintos sistemas de numeración. Cada sistema tiene su propia base: el binario (base 2), el octal (base 8), el decimal (base 10) y el hexadecimal (base 16). Estas conversiones son fundamentales para trabajar con datos en distintos niveles de abstracción en las áreas de la informática y la electrónica.

# Capítulo 2: Álgebra de Boole:

• El álgebra Booleana es una rama de las matemáticas que se utiliza para el análisis y diseño de circuitos digitales. Emplea variables binarias y operaciones lógicas como AND, OR y NOT, permitiendo simplificar y optimizar circuitos lógicos con el fin de reducir costos en su implementación y mejorar su eficiencia.

# Capítulo 3: Operaciones Lógicas Binarias:

- Este capítulo muestra con ejemplos sobre cómo realizar operaciones aritméticas básicas como la suma, la resta, la multiplicación y la división utilizando números binarios. Es esencial para entender el funcionamiento interno de los microprocesadores y otros componentes digitales.

- o Se exploran los circuitos lógicos para llevar a cabo operaciones con números binarios como: sumadores, restadores, multiplicadores y divisores, que son bloques fundamentales en la construcción de unidades aritméticológicas (ALU) en computadoras.

# Capítulo 4: Funciones Lógicas:

o Este capítulo se enfoca en ejemplos que develan el procedimiento y solución de funciones lógicas utilizando los diferentes tipos de compuertas lógicas, sus expresiones Booleanas, tablas de verdad y la simbología propia de cada tipo.

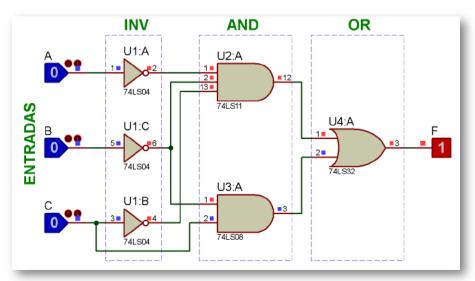

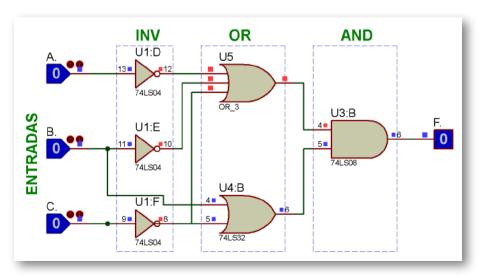

# Capítulo 5: Minterm y Maxterm, Lógica AOI:

• La lógica AOI (AND-OR-NOT) es una técnica utilizada para implementar funciones lógicas. Los minterms y maxterms son representaciones canónicas de funciones Booleanas que se emplean para estructurar el diseño de circuitos lógicos con base en solo compuertas lógicas AND, NOT y OR y que simplifican el diseño e implementación.

# Capítulo 6: Mapas de Karnaugh:

o Los mapas de Karnaugh son una herramienta gráfica utilizada para simplificar funciones lógicas de manera visual. inventada por el físico matemático Maurice estadounidense Karnaugh. Facilitan minimización de expresiones Booleanas, ayudando a diseñar circuitos más sencillos y eficaces.

Cada capítulo contiene una serie de Videos explicativos, Objetos Interactivos, archivos con Simulaciones y Hojas de Datos de los circuitos integrados, diseñados para complementar y enriquecer el aprendizaje. Estos recursos adicionales permiten al lector visualizar y experimentar con los conceptos en un entorno dinámico y práctico que enriquecen la experiencia de aprendizaje al proporcionar una perspectiva práctica y aplicable; donde, cada uno de estos temas es crucial para desarrollar una comprensión sólida de la Electrónica Digital. En la parte final del libro encuentra unas actividades de sirven Repaso de autoexamen para comprobar que conocimientos y la comprensión de los temas trabajados; igualmente. varios Anexos como información complementaria.

Invito a los lectores a sumergirse en este viaje de exploración y descubrimiento, utilizando los ejemplos resueltos y los ejercicios propuestos como una guía para alcanzar una comprensión profunda y aplicada del mundo de la Electrónica Digital. Espero que este libro se convierta en un aliado indispensable en su formación y desarrollo profesional.

> Oscar Ignacio Botero Henao **Autor**

# Capítulo I

Conversiones: Sistemas Numéricos

#### 1.1 Conversión de Decimal a Binario

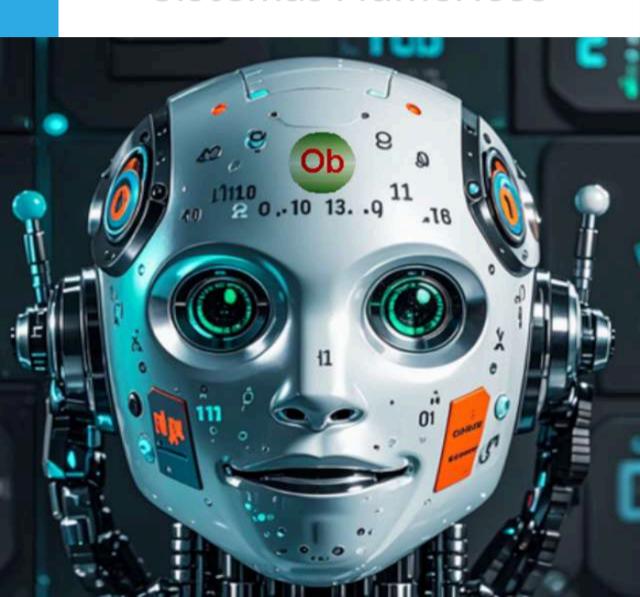

Para la conversión de la parte entera, se va dividiendo la cantidad decimal por la base 2 (divisiones sucesivas), tantas veces como sea posible, hasta que llegar a un cociente de 1. Luego, se toma el último "Cociente" y todos los "Residuos" comenzando con el último (bit más significativo - MSB) hasta llegar al primero (bit menos significativo - LSB) como lo indica la flecha en la figura.[1][2][3][4][5][7]

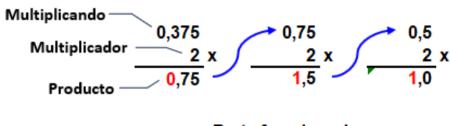

Para la conversión de la parte fraccionaria se multiplica sucesivamente por la base 2, hasta la cantidad de dígitos fraccionarios que se requieran o hasta que el resultado del producto sea cero (0); para la respuesta se toman los valores enteros de cada producto y los valores que sobran se siguen multiplicando por 2.

#### ★ Ejemplo 1: ¿Convertir 27,375<sub>d</sub> a binario?

Otra forma de evidenciar la solución es:

$$27 \div 2 = 13 \text{ y residuo } 1$$

$$13 \div 2 = 6$$

y residuo **1**

$$6 \div 2 = 3$$

y residuo 0

$3 \div 2 = 1$  y residuo 1

Parte entera = 11011<sub>b</sub>

Para la parte fraccionaria se utiliza la multiplicación:

#### Parte fraccionaria 011<sub>h</sub>

Otra forma de evidenciar la solución es:

#### ★ Ejemplo 2: ¿Convertir 103,85<sub>10</sub> a binario?

$$103 \div 2 = 51$$

y residuo 1

$51 \div 2 = 25$  y residuo 1

$25 \div 2 = 12$  y residuo 1

$12 \div 2 = 6$  y residuo 0

$6 \div 2 = 3$  y residuo 0

$3 \div 2 = 1$  y residuo 1

Parte entera = 1100111<sub>b</sub>

```

0,85 x 2 = 1 y residuo 7

0,7 x 2 = 1 y residuo 4

0,4 x 2 = 0 y residuo 8

0,8 x 2 = 1 y residuo 6

0,6 x 2 = 1 y residuo 2

0,2 x 2 = 0 y residuo 4 y se repiten las operaciones a partir del residuo 4

Parte fraccionaria = 110110<sub>b</sub>

► R/. 103,85<sub>d</sub> = 1100111,110110<sub>b</sub> ✓

```

#### 1.2 Conversión de Binario a Decimal

Para la conversión se utiliza el "método de la suma de pesos o ponderaciones", donde se toman los dígitos de la parte entera de derecha a izquierdo y se multiplica cada dígito por 2 elevado a la potencia correspondiente, comenzando con 2º e incrementando en uno (1) el valor de la potencia, a esto se le denomina "ponderar cada digito"; luego, se realiza la suma de todos los resultados parciales de la parte entera. Para la parte fraccionaria, se toman los dígitos de izquierda a derecha con exponentes negativos comenzando con 2º¹ y se multiplica por cada dígito que está en esa posición; finalmente, se suman los resultados parciales de la parte fraccionaria. El resultado final es la unión de los dos resultados.

#### ★ Ejemplo 1: ¿Convertir 101,011<sub>h</sub> a decimal?

#### ★ Ejemplo 2: ¿Convertir 1101,101<sub>b</sub> a decimal?

$$1 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 1 \times 2^{0} + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}$$

$1 \times 8 + 1 \times 4 + 0 \times 2 + 1 \times 1 + 1 \times 1/2 + 0 \times 1/4 + 1 \times 1/8$

$8 + 4 + 1 + 1/2 + 1/8$

$8 + 4 + 1 + 0.5 + 0.125$

$\triangleright R/. 1101,101_{b} = 13,625_{d}$

#### 1.3 Conversión de Decimal a Octal

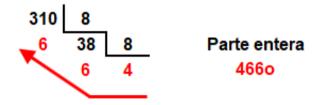

Para la conversión de la parte entera, se va dividiendo la cantidad decimal por la base 8 (divisiones sucesivas), tantas veces como sea posible, hasta que llegar a un cociente menor que 8.

Luego, se toma el último "Cociente" y todos los "Residuos" comenzando con el último (bit más significativo - MSB) hasta llegar al primero (bit menos significativo - LSB) como lo indica la flecha en la siguiente figura.

#### ★ Ejemplo 1: ¿Convertir 310,625<sub>d</sub> a octal?

Otra forma de evidenciar la solución es:

$$310 \div 8 = 38 \text{ y residuo } 6$$

$38 \div 8 = 4 \text{ y residuo } 6$

Parte entera = 466

Para la parte fraccionaria se utiliza la multiplicación:

★ Ejemplo 2: ¿Convertir 415,75<sub>d</sub> a octal?

Parte fraccionaria =

$$6_0$$

$\triangleright$  R/. 415,75<sub>d</sub> = 637,6<sub>o</sub>  $\checkmark$

### 1.4 Conversión de Octal a Decimal

Para la conversión se utiliza el "método de la suma de pesos o ponderaciones".

Para la conversión de Octal a Decimal, se toman los dígitos de la parte entera de derecha a izquierda y se multiplica cada dígito por 8 elevado a la potencia correspondiente, comenzando con 8º e incrementando en uno (1) el valor de la potencia, a esto se le denomina "ponderar cada dígito"; luego, se realiza la suma de todos los resultados parciales de la parte entera. Para la parte fraccionaria, se toman los dígitos de izquierda a derecha con exponentes negativos

comenzando con 8<sup>-1</sup> y se multiplica por cada dígito que está en esa posición; finalmente, se suman los resultados parciales de la parte fraccionaria. El resultado final es la unión de los dos resultados.

#### ★ Ejemplo 1: ¿Convertir 521,043° a decimal?

$$5 \times 8^{2} + 2 \times 8^{1} + 1 \times 8^{0} + 0 \times 8^{-1} + 4 \times 8^{-2} + 3 \times 8^{-3}$$

$5 \times 64 + 2 \times 8 + 1 \times 1 + 0 \times 1/8 + 4 \times 1/64 + 3 \times 1/512$

$320 + 16 + 1 + 0,0625 + 0,005859375$

$\nearrow R/. 521,043_{0} = 337,068359375_{d} \checkmark$

#### ★ Ejemplo 2: ¿Convertir 713,51° a decimal?

```

7 \times 8^{2} + 1 \times 8^{1} + 3 \times 8^{0} + 5 \times 8^{-1} + 1 \times 8^{-2}

7 \times 64 + 1 \times 8 + 3 \times 1 + 5 \times 1/8 + 1 \times 1/64

448 + 8 + 3 + 0,625 + 0,015625

\triangleright R/.713,51_{o} = 459,640625_{d} \checkmark

```

#### 1.5 Conversión de Decimal a Hexadecimal

Para la conversión de la parte entera, se va dividiendo la cantidad decimal por la base 16 (divisiones sucesivas), tantas veces como sea posible, hasta que llegar a un cociente menor que 16. Luego, se toma el último "Cociente" y todos los "Residuos" comenzando con el último (bit más significativo - MSB) hasta llegar al primero (bit menos significativo - LSB) como lo indica la flecha en la siguiente figura.

#### ★ Ejemplo 1: ¿Convertir 158,25<sub>d</sub> a hexadecimal?

Otra forma de evidenciar la solución es:

158 ÷ 16 =

$$\frac{9}{9}$$

y residuo  $\frac{14}{-->}$  E Parte entera =  $\frac{9}{E_h}$

0,25 x 16 = 4 y residuo 0

Parte fraccionaria =

$$4_h$$

$R/. 158,25_d = 9E,4_h$

★ Ejemplo 2: ¿Convertir 92,15<sub>d</sub> a hexadecimal?

#### 1.6 Conversión de Hexadecimal a Decimal

Para la conversión se utiliza el "método de la suma de pesos o ponderaciones".

Para la conversión de Hexadecimal a Decimal, se toman los dígitos de la parte entera de derecha a izquierda y se multiplica cada dígito por 16 elevado a la potencia correspondiente, comenzando con 16<sup>0</sup> e incrementando en uno (1) el valor de la potencia, a esto se le denomina "ponderar cada dígito"; luego, se realiza la suma de todos los resultados parciales de la parte entera. Para la parte fraccionaria, se toman los dígitos de izquierda a derecha con exponentes negativos comenzando con 16<sup>-1</sup> y se multiplica por cada dígito que está en esa posición; finalmente, se suman los resultados parciales de la parte fraccionaria. El resultado final es la unión de los dos resultados parciales.

#### ★ Ejemplo 1: ¿Convertir 3AF,D<sub>h</sub> a decimal?

$$3 \times 16^{2} + A \times 16^{1} + F \times 16^{0} + D \times 16^{-1}$$

$3 \times 256 + 10 \times 16 + 15 \times 1 + 13 \times 1/16$

$768 + 160 + 15 + 0,8125$

$\nearrow R/. 3AF,D_h = 943,8125_d$

#### ★ Ejemplo 2: ¿Convertir ABC,37<sub>h</sub> a decimal?

A x

$$16^2$$

+ B x  $16^1$  + C x  $16^0$  + 3 x  $16^{-1}$  + 7 x  $16^{-2}$

$10 \times 256 + 11 \times 16 + 12 \times 1 + 3 \times 1/16 + 7 \times 1/256$

$2560 + 176 + 12 + 0,1875 + 0,02734375$

> R/. ABC,37<sub>b</sub> = 2748,21484375<sub>d</sub>

#### 1.7 Conversión de Binario a Octal

Este método consiste en agrupar de a tres (3) bits. Para la parte entera se comienza de derecha a izquierda, o sea del bit menos significativo (LSB) hasta el más significativo (MSB), para la parte fraccionaria se agrupan en sentido contrario (de izquierda a derecha). Cuando las cifras no están completas, o sea de a tres (3) bits se completan con ceros (0) a la izquierda para la parte entera y con ceros a la derecha para la parte fraccionaria.

110011101,001101B

$$\rightarrow$$

Oct

110 011 101, 001 101B  $\rightarrow$  635,150

421 421 421 421 421

★ Ejemplo 1: ¿Convertir 1001011011,1010<sub>b</sub> a octal?

Parte entera:  $001001011011_b$ , agrupados de a 3 bits =  $1133_o$

Parte fraccionaria:  $101000_h$ , agrupados de a 3 bits =  $50_o$

$$ightharpoonup$$

R/. 1001011011,1010<sub>b</sub> = 1133,50<sub>a</sub>  $\checkmark$

★ Ejemplo 2: ¿Convertir 111010011,101011<sub>b</sub> a octal?

Parte entera:  $111\,010\,011_b$ , agrupados de a 3 bits =  $7\,2\,3_o$ Parte fraccionaria:  $101\,011_b$ , agrupados de a 3 bits =  $5\,3_o$

$$ightharpoonup$$

R/. 111010011,101011<sub>b</sub> = 723,53<sub>o</sub>  $\checkmark$

#### 1.8 Conversión de Octal a Binario

Cada carácter octal se representa en 3 bits, tanto para la parte entera como para la parte fraccionaria.

#### ★ Ejemplo 1: ¿Convertir 37,61° a binario?

Parte entera:  $37_o$ , representados en 3 bits cada carácter =  $011\ 111_b$ Parte fraccionaria:  $61_o$ , representados en 3 bits cada carácter =  $110\ 001_b$

$$ightharpoonup$$

R/. 37,61<sub>o</sub> = 011111,110001<sub>b</sub>  $\checkmark$

#### ★ Ejemplo 2: ¿Convertir 152,731° a binario?

Parte entera:  $152_o$ , representados en 3 bits cada carácter =  $001\ 101$   $010_b$

Parte fraccionaria:  $731_o$ , representados en 3 bits cada carácter = 111  $011001_b$

$$ightharpoonup$$

R/. 152,731<sub>o</sub> = 1101010,111011001<sub>b</sub>  $\checkmark$

#### 1.9 Conversión de Binario a Hexadecimal

Este método es similar a la conversión de Binario a Octal, pero agrupando de a cuatro (4) bits.

Para la parte entera se comienza de derecha a izquierda, o sea del bit menos significativo (LSB) hasta el más significativo (MSB), para la parte fraccionaria se procede a agrupar en sentido contrario, o sea de izquierda a derecha. Cuando las cifras no están completas, o sea de a cuatro (4) bits se completan con ceros (0) a la izquierda para la parte entera y con ceros a la derecha para la parte fraccionaria.

#### ★ Ejemplo 1: ¿Convertir 1101101111,101011<sub>b</sub> a hexadecimal?

Parte entera:  $11\,0110\,1111_b$ , agrupados en 4 bits =  $36F_h$ Parte fraccionaria:  $1010\,11_b$ , agrupados en 4 bits =  $AC_h$

ightharpoonup R/. 1101101111,101011<sub>b</sub> = 36F,AC<sub>h</sub>  $\checkmark$

★ Ejemplo 2: ¿Convertir 111101011,1000101<sub>b</sub> a hexadecimal?

Parte entera: 1 1110 1011<sub>b</sub>, agrupados en 4 bits =  $1EB_h$ Parte fraccionaria: 1000 101<sub>b</sub>, agrupados en 4 bits =  $8A_h$

ightharpoonup R/. 111101011,1000101<sub>b</sub> = 1EB,8A<sub>b</sub>  $\checkmark$

#### 1.10 Conversión de Hexadecimal a Binario

Cada carácter hexadecimal se representa en 4 bits, tanto para la parte entera como la fraccionaria; similar a la conversión de octal a binario.

#### ★ Ejemplo 1: ¿Convertir A46,1F<sub>h</sub> a binario?

Parte entera:  $A46_h$ , representada en 4 bits =  $1010\,0100\,0110_b$ Parte fraccionaria:  $1F_h$ , representada en 4 bits =  $0001\,1111_b$

ightharpoonup R/. A46,1F<sub>b</sub> = 1010 0100 0110,0001 1111<sub>b</sub>  $\checkmark$

#### ★ Ejemplo 2: ¿Convertir 356,01<sub>h</sub> a binario?

Parte entera:  $356_h$ , representada en 4 bits =  $11\,0101\,0110_b$ Parte fraccionaria:  $01_h$ , representada en 4 bits =  $0000\,0001_h$

ightharpoonup R/. 356,01<sub>h</sub> = 11 0101 0110,0000 0001<sub>b</sub>  $\checkmark$

#### 1.11 Conversión de Octal a Hexadecimal

Para la conversión se realizan dos pasos, primero se convierte de Octal a Decimal y luego de Decimal a Hexadecimal.

#### ★ Ejemplo 1: ¿Convertir 147,25° a hexadecimal?

$$1 \times 8^{2} + 4 \times 8^{1} + 7 \times 8^{0} + 2 \times 8^{-1} + 5 \times 8^{-2}$$

$1 \times 64 + 4 \times 8 + 7 \times 1 + 2 \times 1/8 + 5 \times 1/64$

#### Ahora, se convierte de Decimal a Hexadecimal:

103 ÷ 16 = 6 y residuo 7

Parte entera =

$$67_h$$

0,328125 x 16 = 5 y residuo 25

0,25 x 16 = 4 y residuo 0

Parte fraccionaria =  $0.54_h$

R/. 103,328125<sub>d</sub> =  $60.54_h$

$\sim$  R/. 147,25<sub>o</sub> =  $60.54_h$

#### ★ Ejemplo 2: ¿Convertir 100,75° a hexadecimal?

$$1 \times 8^{2} + 0 \times 8^{1} + 0 \times 8^{0} + 7 \times 8^{-1} + 5 \times 8^{-2}$$

$1 \times 64 + 0 \times 8 + 0 \times 1 + 7 \times 1/8 + 5 \times 1/64$

$64 + 0.875 + 0.078125$

**R/.**  $100.75_{0} = 64.953125_{d}$

Ahora, se convierte de Decimal a Hexadecimal:

$64 \div 16 = 4$  y residuo 0

#### 1.12 Conversión de Hexadecimal a Octal

Para la conversión se realizan dos pasos, primero se convierte de Hexadecimal a Decimal y luego de Decimal a Octal.

#### ★ Ejemplo 1: ¿Convertir 1A7,5<sub>h</sub> a octal?

```

1 \times 16^{2} + A \times 16^{1} + 7 \times 16^{0} + 5 \times 16^{-1}

1 \times 256 + 10 \times 16 + 7 \times 1 + 5 \times 1/16

256 + 160 + 7 + 0,3125

R/. 1A7,5<sub>h</sub> = 423,3125<sub>d</sub>

```

Ahora, se convierte de Decimal a Octal:

#### ★ Ejemplo 2: ¿Convertir 61D,3<sub>h</sub> a octal?

$$6 \times 16^{2} + 1 \times 16^{1} + D \times 16^{0} + 3 \times 16^{-1}$$

$6 \times 256 + 1 \times 16 + 13 \times 1 + 3 \times 1/16$

$1536 + 16 + 13 + 0,1875$

**R/. 61D,3**<sub>h</sub> = **1565,1875**<sub>d</sub>

#### Ahora, se convierte de Decimal a Octal:

```

195 ÷ 8 = 24 y residuo 3

24 ÷ 8 = 3 y residuo 0

Parte entera = 3035<sub>o</sub>

0,1875 x 8 = 1 y residuo 5

0,5 x 8 = 4 y residuo 0

Parte fraccionaria = 14<sub>o</sub>

R/. 1565,1875<sub>d</sub> = 3035,14<sub>o</sub> ✓

```

$1565 \div 8 = 195 \text{ y residuo } 5$

# 1.13 Ejercicios propuestos con respuesta

#### 1.13.1 Decimal a Binario

- 1. ¿Convertir 91,12<sub>d</sub> a binario? **R/. 1011011,000111**<sub>b</sub>

- 2. ¿Convertir 146,56<sub>d</sub> a binario? **R/. 10010010,10001111**<sub>b</sub>

- 3. ¿Convertir  $82,55_d$  a binario? **R/. 1010010,1000110**<sub>b</sub>

- 4. ¿Convertir 200,62<sub>d</sub> a binario? **R/. 11001000,10011110101**<sub>h</sub>

- 5. ¿Convertir 169,48<sub>d</sub> a binario? **R/. 10101001,011110101**<sub>b</sub>

#### 1.13.2 Binario a Decimal

- 1. ¿Convertir 11010011,01101<sub>b</sub> a decimal? **R/. 211,40625**<sub>d</sub>

- 2. ¿Convertir 1000110010,101<sub>b</sub> a decimal? **R/. 562,625**<sub>d</sub>

- 3. ¿Convertir 1001101110,1101, a decimal? R/. 622,8125<sub>d</sub>

- 4. ¿Convertir 101010101,11111<sub>b</sub> a decimal? R/. 341,9375<sub>d</sub>

- 5. ¿Convertir 11001111,111 $_b$  a decimal? R/. 207,875 $_d$

#### 1.13.3 Decimal a Octal

- 1. ¿Convertir 84,15<sub>d</sub> a octal? **R/. 124,114**<sub>o</sub>

- 2. ¿Convertir 125,3<sub>d</sub> a octal? **R/. 175,231463**<sub>o</sub>

- 3. ¿Convertir 142,75<sub>d</sub> a octal? **R/. 216,6**<sub>0</sub>

- 4. ¿Convertir 452,06<sub>d</sub> a octal? **R/. 704,036560507**<sub>o</sub>

- 5. ¿Convertir 700,33<sub>d</sub> a octal? R/. 1274,250753412<sub>o</sub>

#### 1.13.4 Octal a Decimal

- 1. ¿Convertir 157,31<sub>o</sub> a decimal? R/. 111,390625<sub>d</sub>

- 2. ¿Convertir 740,123<sub>o</sub> a decimal? **R/. 480,1621094**<sub>d</sub>

- 3. ¿Convertir 333,333<sub>0</sub> a decimal? **R/. 219,4277344**<sub>d</sub>

- 4. ¿Convertir 1005,462<sub>o</sub> a decimal? **R/. 517,5976563**<sub>d</sub>

- 5. ¿Convertir 2100,504<sub>o</sub> a decimal? **R/. 1088,632813**<sub>d</sub>

#### 1.13.5 Decimal a Hexadecimal

- 1. ¿Convertir 101,8<sub>d</sub> a hexadecimal? R/. 65,CCC<sub>h</sub>

- 2. ¿Convertir 197,8125<sub>d</sub> a hexadecimal? R/. C5,D<sub>h</sub>

- 3. ¿Convertir 222,46<sub>d</sub> a hexadecimal? R/. DE,75C28F5C28<sub>h</sub>

- 4. ¿Convertir 415,68<sub>d</sub> a hexadecimal? R/. 19F,AE147AE147<sub>h</sub>

- 5. ¿Convertir 375,208<sub>d</sub> a hexadecimal? R/. 177,353F7CED91<sub>h</sub>

#### 1.13.6 Hexadecimal a Decimal

- 1. ¿Convertir 9B0,D1<sub>h</sub> a decimal? **R/. 2480,816406**<sub>d</sub>

- 2. ¿Convertir FEA,7 $C_h$  a decimal? **R/.** 4074,484375<sub>d</sub>

- 3. ¿Convertir 824,B1<sub>h</sub> a decimal? **R/. 2084,691406**<sub>d</sub>

- 4. ¿Convertir CE5,0F<sub>h</sub> a decimal? **R/. 3301,058594**<sub>d</sub>

- 5. ¿Convertir DEA,31<sub>h</sub> a decimal? **R/. 3562,191406**<sub>d</sub>

#### 1.13.7 Binario a Octal

- 1. ¿Convertir 1 010 111,111 01<sub>b</sub> a octal? **R/. 127,72**<sub>o</sub>

- 2. ¿Convertir 101 0101 110,001 111 01<sub>b</sub> a octal? R/. 1256,172<sub>o</sub>

- 3. ¿Convertir 10 000 110 110,110 000 11<sub>b</sub> octal? R/. 2066,606<sub>o</sub>

- 4. ¿Convertir 11 111 110 011,101 010  $10_b$  a octal? **R/.** 3763,524°

- 5. ¿Convertir 1 100 000 001,100 01<sub>b</sub> a octal? **R/. 1401,42**<sub>o</sub>

#### 1.13.8 Octal a Binario

1. ¿Convertir 100,707<sub>o</sub> a binario? **R/. 1 000 000,111 000 111**<sub>h</sub>

- 2. ¿Convertir 2530,5541<sub>o</sub> a binario? **R/. 10 101 011 000,101 101 100 001**<sub>b</sub>

- 3. ¿Convertir 1069,2263<sub>o</sub> binario? **R/. 1000 110 011,010 010 110 011**<sub>b</sub>

- 4. ¿Convertir 1313,3131<sub>o</sub> a binario? **R/. 1011001011,011001011001**<sub>b</sub>

- 5. ¿Convertir 5714,265<sub>o</sub> a binario? **R/. 101 111 001 100,010 110 101**<sub>h</sub>

#### 1.13.9 Binario a Hexadecimal

- 1. ¿Convertir 1001000111,1100101<sub>b</sub> a hexadecimal? **R/. 247,CA**<sub>h</sub>

- 2. ¿Convertir 11110000011001,0011100011<sub>b</sub> a hexadecimal? **R/. 3C19,38C**<sub>h</sub>

- 3. ¿Convertir 100000011111,0001011110<sub>b</sub> a hexadecimal? **R/. 81F,178**<sub>b</sub>

- 4. ¿Convertir 100111000001,010011001101<sub>b</sub> a hexadecimal? **R/.** 9C1,4CD<sub>b</sub>

- 5. ¿Convertir 11111111111101,00000111011<sub>b</sub> a hexadecimal? **R/. 1FFD,076**<sub>b</sub>

#### 1.13.10 Hexadecimal a Binario

¿Convertir 664,E23<sub>h</sub> a binario?

R/. 0110 0110 0100,1110 0010 0011<sub>h</sub>

- 2. ¿Convertir 126,D73<sub>h</sub> a binario? **R/. 0001 0010 0110, 1101 0111 0011**<sub>h</sub>

- ¿Convertir 430,CD1<sub>h</sub> a binario?

R/. 0100 0011 0000,1100 1101 0001<sub>b</sub>

- 4. ¿Convertir 987,654<sub>h</sub> a binario? **R/. 1001 1000 0111,0110 0101 0100**<sub>h</sub>

- 5. ¿Convertir 61F,308<sub>h</sub> a binario? **R/. 0110 0001 1111,0011 0000 1000**<sub>h</sub>

#### 1.13.11 Octal a Hexadecimal

- 1. ¿Convertir 465,25<sub>o</sub> a hexadecimal? **R/. 135,54**<sub>b</sub>

- 2. ¿Convertir 71,32 $_{o}$  a hexadecimal? **R/. 39,68**<sub>h</sub>

- 3. ¿Convertir 2407,53<sub>o</sub> a hexadecimal? **R/. 507,AC**<sub>h</sub>

- 4. ¿Convertir 3562,17<sub>o</sub> a hexadecimal? **R/. 772,3C**<sub>b</sub>

- 5. ¿Convertir  $5371,06_o$  a hexadecimal? **R/. AF9,18<sub>h</sub>**

#### 1.13.12 Hexadecimal a Octal

1. ¿Convertir 381,0A<sub>h</sub> a octal? **R/. 1601,024**<sub>o</sub>

2. ¿Convertir 6E9,B5<sub>h</sub> a octal? **R/. 3351,552**<sub>o</sub>

3. ¿Convertir 41B,2<sub>h</sub> a octal? **R/. 2033,1**<sub>o</sub>

4. ¿Convertir FEA,03<sub>h</sub> a octal? **R/. 7752,006**<sub>o</sub>

¿Convertir 58,9<sub>h</sub> a octal?

R/. 130,44<sub>o</sub>

COMPLEMENTOS

# 1.14 Videos

#### Vídeos sobre conversiones del sistema Decimal:<sup>1</sup>

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de DECIMAL a BINARIO con PARTE FRACCIONARIA - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de DECIMAL a OCTAL con PARTE FRACCIONARIA - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de DECIMAL a HEXADECIMAL con PARTE FRACCIONARIA - Ejercicio #1", licencia de atribución de Creative Commons.

<sup>&</sup>lt;sup>1</sup> Videos realizados por Marisol Maldonado Olmos (*Pasos por Ingeniería*), <u>CONVERSIÓN</u> entre sistemas numéricos...

#### Vídeos sobre conversiones del sistema Binario:<sup>2</sup>

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de BINARIO a OCTAL - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de BINARIO a DECIMAL con PARTE FRACCIONARIA - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (*Pasos por Ingeniería*), titulado "CONVERTIR de BINARIO a HEXADECIMAL - Ejercicio #1", licencia de atribución de Creative Commons.

<sup>&</sup>lt;sup>2</sup> Videos realizados por Marisol Maldonado Olmos (*Pasos por Ingeniería*), <u>CONVERSIÓN</u> entre sistemas numéricos...

#### Vídeos sobre conversiones del sistema Hexadecimal:<sup>3</sup>

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de HEXADECIMAL a BINARIO - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de HEXADECIMAL a OCTAL - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de HEXADECIMAL a DECIMAL con PARTE FRACCIONARIA - Ejercicio #1", licencia de atribución de Creative Commons.

<sup>&</sup>lt;sup>3</sup> Videos realizados por Marisol Maldonado Olmos (*Pasos por Ingeniería*), <u>CONVERSIÓN</u> entre sistemas numéricos...

#### Vídeos sobre conversiones del sistema Octal:4

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de OCTAL a BINARIO - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de OCTAL a DECIMAL con PARTE FRACCIONARIA - Ejercicio #1", licencia de atribución de Creative Commons.

Video realizado por Marisol Maldonado Olmos (Pasos por Ingeniería), titulado "CONVERTIR de OCTAL a HEXADECIMAL - Ejercicio #1", licencia de atribución de Creative Commons.

<sup>&</sup>lt;sup>4</sup> Videos realizados por Marisol Maldonado Olmos (*Pasos por Ingeniería*), <u>CONVERSIÓN</u> entre sistemas numéricos...

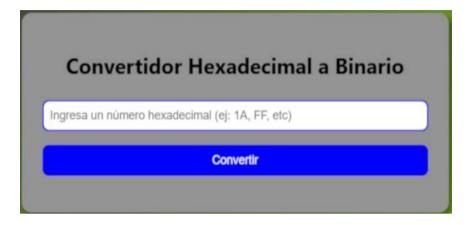

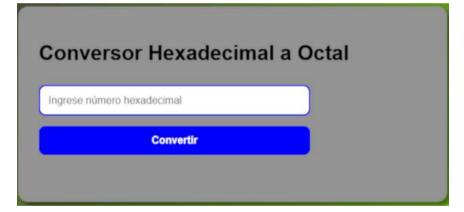

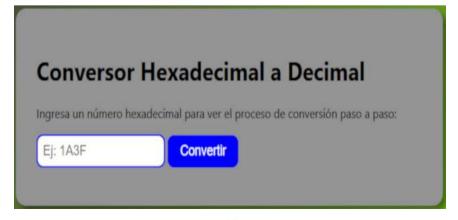

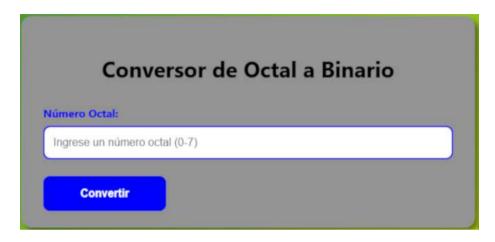

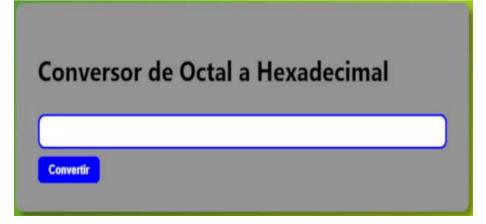

# 1.15 Objetos Interactivos

## Haga clic sobre la imagen para abrir el objeto interactivo:

Estos objetos interactivos fueron generados con la *asistencia* de la Inteligencia Artificial (IA) en el sitio: <a href="https://websim.ai/">https://websim.ai/</a>

# Convertidores partiendo del sistema Binario:

## Convertidores partiendo del sistema Decimal:

## Convertidores partiendo del sistema Hexadecimal:

#### Convertidores partiendo del sistema Octal:

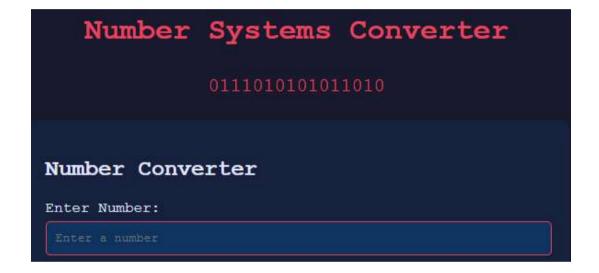

## Convertidor entre los sistemas numéricos Binario, Decimal y Hexadecimal

Objeto Interactivo para la conversión de valores enteros entre los sistemas numéricos Binario, Decimal y Hexadecimal.<sup>5</sup>

Objeto Interactivo generado con la asistencia de la Inteligencia Artificial (IA) por "Websim.ai", Convertidor de Sistemas Numéricos

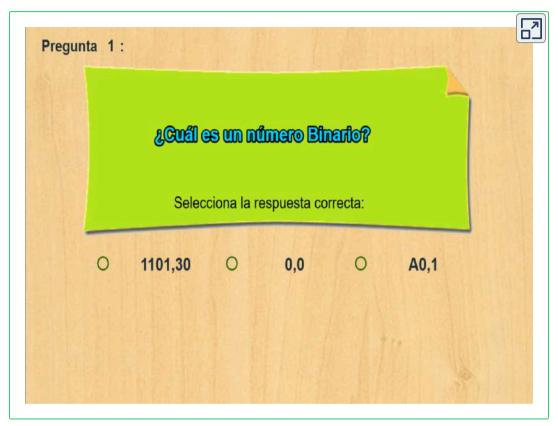

## Seleccione la opción correcta

Objeto Interactivo de selección múltiple con una única respuesta: 6

<sup>&</sup>lt;sup>6</sup> Plantilla del Objeto Interactivo obtenida del sitio web del Proyecto Descartes, intervenida por Oscar Ignacio Botero Henao. Plantillas con Descartes JS

# Capítulo II

Álgebra de Boole

El álgebra de Boole se utiliza para representar en forma de ecuaciones un circuito de lógica digital y de esta forma poder solucionarlos.[2][3][4][5]

| Regla | Nombre                      | Fórmula                                                    |

|-------|-----------------------------|------------------------------------------------------------|

| 1     | Leyes del producto          | A 	imes 0 = 0                                              |

| 2     | Leyes del producto          | A 	imes 1 = A                                              |

| 3     | Lovos do la suma            | A+0=A                                                      |

| 4     | Leyes de la suma            | A+1=1                                                      |

| 5     | Leyes de la                 | A 	imes A = A                                              |

| 6     | tautología                  | A+A=A                                                      |

| 7     | Leyes de los                | $A	imes \overline{A}=0$                                    |

| 8     | complementos                | $A+\overline{A}=1$                                         |

| 9     | Ley de la doble<br>negación | $\overline{\overline{A}}=A$                                |

| 10    | Leyes                       | A 	imes B = B 	imes A                                      |

| 11    | conmutativas                | A+B=B+A                                                    |

| 12    | Lovos distributivos         | A 	imes (B+C) = AB + AC                                    |

| 13    | Leyes distributivas         | A+BC=(A+B)	imes (A+C)                                      |

| 14    |                             | $ABC = (AB) \times C = A \times (BC)$<br>= $(AC) \times B$ |

| 15    | Leyes asociativas           | A + B + C = (A + B) + C<br>= $A + (B + C) = (A + C) + B$   |

Tabla: Leyes básicas del Álgebra de Boole

| Regla | Nombre                | Fórmula                                              |

|-------|-----------------------|------------------------------------------------------|

| 16    | Leyes de<br>absorción | $A\times (A+B)=A$                                    |

| 17    |                       | $A+(A\times B)=A$                                    |

| 18    |                       | $A	imes (\overline{A}+B)=A	imes B$                   |

| 19    |                       | $\overline{A} 	imes (A+B) = \overline{A} 	imes B$    |

| 20    |                       | $\overline{A} + (A 	imes B) = \overline{A} + B$      |

| 21    |                       | $A+(\overline{A}\times B)=A+B$                       |

| 22    |                       | $A+(\overline{A}	imes\overline{B})=A+\overline{B}$   |

| 23    |                       | $(A+B)\times (A+\overline{B})=A$                     |

| 24    |                       | $(A\times B)+(A\times \overline{B})=A$               |

| 25    | Lovos do Morgos       | $\overline{A+B}=\overline{A}	imes\overline{B}$       |

| 26    | Leyes de Morgan       | $\overline{A 	imes B} = \overline{A} + \overline{B}$ |

Tabla: CONTINUACIÓN: Leyes básicas del Álgebra de Boole

# 2.1 Demostración de las Reglas de Absorción

Regla 16: aplicar la regla 12 (ley distributiva)

$$F = A \times (A + B)$$

$\therefore$   $F = (A \times A) + (A \times B)$

$$F = (A) + (A \times B) \therefore F = A(1 + B)$$

$$F = A \times 1 \therefore \mathbf{F} = \mathbf{A}$$

**Regla 17:** sacar factor común A

$$F = A + (A \times B) : F = A(1+B) : F = A$$

Regla 18: aplicar la regla 12 (ley distributiva)

$$F = A \times (\overline{A} + B) : F = (A \times \overline{A}) + (A \times B)$$

$F = 0 + (A \times B) : F = A \times B$

Regla 19: aplicar la regla 12 (ley distributiva)

$$F = \overline{A} \times (A + B) : F = (\overline{A} \times A) + (\overline{A} \times B)$$

$F = 0 + (A \times B) : F = A \times B$

Regla 20: aplicar la regla 13 (ley distributiva)

$$F = \overline{A} + (A \times B) : F = (\overline{A} + A) \times (\overline{A} + B)$$

$F = 1 \times (\overline{A} + B) : F = \overline{A} + B$

Regla 21: aplicar la regla 13 (ley distributiva)

$$F = A + (\overline{A} \times B) : F = (A + \overline{A}) \times (A + B)$$

$F = 1 \times (A + B) : F = A + B$

Regla 22: aplicar la regla 13 (ley distributiva)

$$F = A + (\overline{A} \times \overline{B}) : F = (A + \overline{A}) \times (A + \overline{B})$$

$F = 1 \times (A + \overline{B}) : F = A + \overline{B}$

Regla 23: aplicar la regla 12 (ley distributiva)

$$F = (A + B) \times (A + \overline{B})$$

$$F = (A \times A) + (A \times \overline{B}) + (A \times B) + (B \times \overline{B})$$

$$F = A + (A \times \overline{B}) + (A \times B) + 0$$

$$F = A(1 + \overline{B} + B) \therefore \mathbf{F} = \mathbf{A}$$

**Regla 24:** sacar factor común A

$$F = (A \times B) + (A \times \overline{B}) : F = A \times (B + \overline{B})$$

$F = A \times 1 : F = A$

# 2.2 Ejemplos

Solución de los siguientes ejercicios utilizando las reglas del álgebra de Boole:

## **★** Ejemplo 1:

$$X = (A \times B \times C) + (B \times C)$$

$R/. X = (B \times C)$

Sacar factor común  $(B \times C)$ :

$$X = (B \times C) \times (A+1) :: X = (B \times C) \times (1)$$

$$X = (B \times C)$$

## ★ Ejemplo 2:

$$J = X(\overline{X} + Y)$$

$R/. J = (X \times Y)$

$$J = (X \times \overline{X}) + (X \times Y)$$

$$J = (X \times Y)$$

## ★ Ejemplo 3:

$$T = (A \times B) + (A \times B \times C) + (A \times B \times \overline{C})$$

$R/. \quad T = (A \times B)$

Sacar factor común  $(A \times B)$  del segundo y tercer término:

$$T = (A \times B) + (A \times B)(C + \overline{C})$$

$$T = (A \times B) + (A \times B)$$

Aplicar la regla 6:

$$T = (A \times B)$$

# ★ Ejemplo 4:

$$M=(X+Y) imes(X+\overline{Y})$$

$oldsymbol{R}/.\quad oldsymbol{M}=oldsymbol{X}$

$$M = XX + X\overline{Y} + XY + Y\overline{Y}$$

$$M = X + X\overline{Y} + XY$$

Sacar factor común

$$X$$

del segundo y tercer término:

$$M = X + X(\overline{Y} + Y)$$

$$M = X + X$$

:  $M = X$

## ★ Ejemplo 5:

$$J = AB + A(B+C) + (B+C)$$

$$R/. \quad J = B + AC$$

$$J = AB + AB + AC + BB + BC$$

$$J = AB + AC + B + BC$$

Sacar factor común

$$B$$

del primer y tercer término:

$$J = B(A+1) + AC + BC$$

$$J = B + AC + BC$$

Sacar factor común

$$B$$

del primer y tercer término:

$$J = B(1+C) + AC$$

$$J = B + AC$$

## ★ Ejemplo 6:

$$S = A(\overline{B}C + C + \overline{C}D + \overline{C})$$

$R/.$   $S = A$

Solucionar el producto:

$$S = A\overline{B}C + AC + A\overline{C}D + A\overline{C}$$

Sacar factor común AC del primer y segundo término; y  $A\overline{C}$  del tercer y cuarto término:

$$S = AC(\overline{B} + 1) + A\overline{C}(D + 1)$$

Aplicar la regla 4:

$$S = AC + A\overline{C}$$

$\square$  Sacar factor común A:

$$S = A(C + \overline{C})$$

:  $S = A$

## ★ Ejemplo 7:

$$Y = A\overline{B} + BC + B + A\overline{B}C$$

$R/.$   $Y = A + B$

Factor común  $A\overline{B}$  del primero y cuarto término. Factor común B del segundo y tercer término:

$$Y = A\overline{B}(1+C) + B(C+1)$$

$$Y = A\overline{B} + B$$

:  $Y = A + B$

## ★ Ejemplo 8:

$$G = \overline{(A + \overline{B} + C) + (B + \overline{C})}$$

$R/.$   $G = 0$

Aplicar la regla 25 (ley de Morgan):

$$G = \overline{(A + \overline{B} + C)} \times \overline{(B + \overline{C})}$$

Aplicar la regla 26 (ley de Morgan):

$$G = (\overline{A} \times B \times \overline{C}) \times (\overline{B} \times C)$$

:  $G = 0$

## ★ Ejemplo 9:

$$N = \overline{(\overline{A}B + A\overline{B})}$$

$R/.$   $N = \overline{A \oplus B}$

Aplicar la regla 25 (ley de Morgan):

$$N = \overline{(\overline{A} imes B)} imes \overline{(A imes \overline{B})}$$

$$N = (A + \overline{B}) \times (\overline{A} + B)$$

Aplicar la regla 25 (ley de Morgan):

$$N = \overline{(\overline{A} imes B)} imes \overline{(A imes \overline{B})}$$

$$N = (A + \overline{B}) \times (\overline{A} + B)$$

Solucionar el producto:

$$N = A\overline{A} + AB + \overline{A}\overline{B} + \overline{B}B$$

Función lógica de la compuerta XNOR:

$$N=\overline{A\oplus B}$$

## ★ Ejemplo 10:

$$K = \overline{A + \overline{B} + \overline{CD}}$$

$R/.$   $K = \overline{A}BCD$

Aplicar la regla 25 (ley de Morgan):

$$K=\overline{A}BCD$$

# 2.3 Ejercicios propuestos con respuestas

Solucionar los siguientes ejercicios utilizando las reglas del álgebra de Boole (ver la tabla con las leyes básicas del álgebra de Boole):

1.

$$R = \overline{AB} + \overline{AC} + \overline{AB}C$$

$R/.$   $R = \overline{A} + \overline{BC}$

2.  $X = (\overline{A} + B) \times (A + B + D) \times \overline{D}$

$R/.$   $X = B\overline{D}$

3.  $F = (\overline{X} + Y) \times (\overline{X}\overline{Y} + \overline{Z})$

$R/.$   $F = \overline{Y} + Z$

4.  $F = (\overline{X}\overline{Y} + XZ) \times (\overline{X} + \overline{Y}Z)$

$R/.$   $F = \overline{X} + Z$

5.  $F = M(X + Y) + MY + Y(X + Y) + MXY$

$R/.$   $F = MX + Y$

6.  $W = A\overline{B} + A(\overline{B} + C) + B(\overline{B} + C)$

$R/.$   $W = A\overline{B}$

7.  $H = (A + B + C) \times (A + B)$

$R/.$   $H = A + B$

8.  $H = (AB) + A(B + C) + B(B + C)$

$R/.$   $H = B + AC$

9.  $L = (X + Y) \times (\overline{X} + Z) \times (Y + Z)$

$R/.$   $L = XZ + Y(\overline{X} + Z)$

10.  $F = \overline{AB} + \overline{ABC} + C(\overline{B} + A)$

$R/.$   $F = 1$

11.

$$T = \overline{A}(C + D) + \overline{B}(A + D) + \overline{A}\overline{B}\overline{C}$$

$R/. \quad T = (A + \overline{C}\overline{D}) \times B$

12.  $Z = [A\overline{B}(C + BD)] + \overline{A}\overline{B}$

$R/. \quad Z = \overline{B}C$

13.  $P = ABC + AC + C$

$R/. \quad P = C$

14.  $K = \overline{A}\overline{B} + \overline{A}B + A\overline{B} + AB$

$R/. \quad K = 1$

15.  $J = \overline{\overline{XY}}\overline{Z} + XZ$

$R/. \quad J = \overline{Z}$

"No importa qué tan correcto un teorema matemático puede parecer, uno nunca debe estar convencido de que no había algo imperfecto en ello hasta que también da la impresión de ser hermosa".

George Boole

# 2.4 Videos

## Haga clic en la esquina superior derecha para expandir el video.

Videos demostrativos sobre la solución de ejercicios con el Álgebra de Boole <sup>7</sup>

Videos realizados por "Les Ingenieurs", <u>Simplificación por ÁLGEBRA BOOLEANA</u> <u>ejercicios [Aprende con 4 ejercicios]</u> y <u>CÓMO Simplificar FUNCIONES BOOLEANAS</u> [Álgebra de Boole] <u>Electrónica Digital</u>

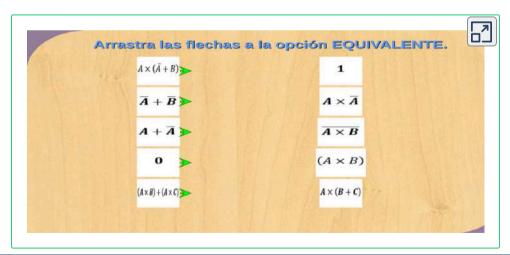

# 2.5 Objetos Interactivos

## Haga clic sobre la imagen para abrir el objeto interactivo:

Objetos Interactivos utilizando el Álgebra Booleana.<sup>8</sup>

<sup>&</sup>lt;sup>8</sup> El primer objeto interactivo fue generado con la *asistencia* de la Inteligencia Artificial (IA) en el sitio: https://websim.ai/. La plantilla del segundo fue obtenida del sitio web del Proyecto Descartes, intervenida por Oscar Ignacio Botero Henao. Plantillas con **DescartesJS**

# Capítulo III

Operaciones Lógicas Binarias

Las *Operaciones Lógicas Binarias* se basan en el *Sistema numérico Binario* y se implementan mediante circuitos lógicos combinacionales que realizan operaciones básicas como: suma, resta, multiplicación y división.[2][3][4][5][6][7][8][9][10]

# 3.1 Suma lógica Binaria

Se suman los dos términos sumandos y si el resultado excede se agrega un '1' a la izquierda del sumando que se está analizando (acarreo = carry).

| Suma Binaria                        |

|-------------------------------------|

| 0+0 = 0                             |

| 0+1 = 1                             |

| 1+0 = 1                             |

| 1+1 = 0 y un acarreo de '1' (carry) |

Tabla: Reglas de la Suma Binaria

Solucionar las siguientes Sumas Binarias y verificar sus resultados con el sistema numérico decimal:

<u>NOTA:</u> para la explicación de los ejemplos, se nombrarán las columnas de derecha a izquierda, así:

$$\longleftarrow$$

## ★ Ejemplo 1:

$$0+0=0$$

$$0+1=1$$

$$1 + 0 = 1$$

$$100 + 010 = 110_b$$

$$4+2=6_d$$

## ★ Ejemplo 2:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$1 + 0 = 1$$

$$1 + 1 = 0$$

$y$   $carry = 1$

Paso 3: se suma el carry anterior con los dos sumandos de C3:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$0 + 0 = 0$$

**Paso 4:** se suma el carry anterior que está en C4:

1

Paso 5: la respuesta binaria de la suma es:

$$101 + 011 = 1000_b$$

Paso 6: verificación en el sistema numérico decimal:

$$5 + 3 = 8_d$$

#### ★ Ejemplo 3:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$1 + 0 = 1$$

$$1 + 1 = 0$$

$y$   $carry = 1$

Paso 3: se suma el carry anterior con los dos sumandos de C3:

$$1 + 0 = 1$$

$$1 + 1 = 0$$

$y$   $carry = 1$

Paso 4: se suma el carry anterior con los dos sumandos de C4:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$0+1=1$$

**Paso 5:** se suma el carry anterior con los dos sumandos de C5:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$0 + 0 = 0$$

**Paso 6:** se suma el carry anterior que está en C6:

1

Paso 7: la respuesta de la suma es:

$$11001 + 01111 = 101000_b$$

Paso 8: verificación en el sistema numérico decimal:

$$25 + 15 = 40_d$$

#### ★ Ejemplo 4:

|   | 1 | 1 | 1 |   | ca | rry |   |   |    |   |

|---|---|---|---|---|----|-----|---|---|----|---|

| 1 | 0 | 1 | 1 | 1 | 0  |     |   | 4 | 6  |   |

|   |   | 1 | 1 | 1 | 0  | +   |   | 1 | 4  | + |

| 1 | 1 | 1 | 1 | 0 | 0  |     | • | 6 | 0d |   |

Paso 1: se suman los sumandos de C1:

$$0 + 0 = 0$$

Paso 2: se suman los dos sumandos de C2:

$$1 + 1 = 0$$

$y$   $carry = 1$

Paso 3: se suma el carry anterior con los dos sumandos de C3:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$0+1=1$$

Paso 4: se suma el carry anterior con los dos sumandos de C4:

$$1+1=0$$

$y$   $carry=1$

$$0+1=1$$

Paso 5: se suma el carry anterior con el sumando de C5:

$$1 + 0 = 1$$

Paso 6: el sumando de C6:

1

Paso 7: la respuesta de la suma es:

$$101110 + 1110 = 111100_b$$

Paso 8: verificación en el sistema numérico decimal:

$$46 + 14 = 60_d$$

#### ★ Ejemplo 5:

|   |   | 1 | 1 | 1 | 1 | 1 | 1 | ca | rry |   |   |                |   |

|---|---|---|---|---|---|---|---|----|-----|---|---|----------------|---|

|   | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1  |     | 1 | 7 | 3              |   |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1  | +   | 2 | 7 | 9              | + |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0  |     | 4 | 5 | 2 <sub>d</sub> |   |

Paso 1: se suman los sumandos de C1:

$$1 + 1 = 0$$

$y$   $carry = 1$

**Paso 2:** se suman los dos sumandos de C2:

$$1 + 0 = 1$$

$$1 + 1 = 0$$

$y$   $carry = 1$

Paso 3: se suma el carry anterior con los dos sumandos de C3:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$0+1=1$$

Paso 4: se suma el carry anterior con los dos sumandos de C4:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$0 + 0 = 0$$

Paso 5: se suma el carry anterior con los dos sumandos de C5:

$$1 + 0 = 1$$

$$1 + 1 = 0$$

$y$   $carry = 1$

Paso 6: se suma el carry anterior con los dos sumandos de C6:

$$1 + 1 = 0$$

$y$   $carry = 1$

$$0 + 0 = 0$$

Paso 7: se suma el carry anterior con los dos sumandos de C7:

$$1 + 0 = 1$$

$$1 + 0 = 1$$

Paso 8: se suman los sumandos de C8:

$$1 + 0 = 1$$

Paso 9: el sumando de C9:

1

Paso 10: la respuesta de la suma es:

$$10101101 + 100010111 = 111000100_b$$

Paso 11: verificación en el sistema numérico decimal:

$$173 + 279 = 452_d$$

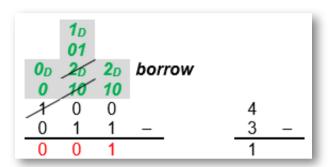

# 3.2 Resta lógica Binaria

Se sustrae del minuendo el sustraendo, entregando como resultado la diferencia; si el sustraendo excede el minuendo se extrae el '1' del minuendo que está a la izquierda convirtiéndose el de la izquierda en '0', equivaliendo el nuevo minuendo que se está analizando al valor  $10_{\rm R} = 2_{\rm D}$ .

| Resta Binaria              |

|----------------------------|

| 0-0 = 0                    |

| 0-1 = 1 y un borrow de '1' |

| 1-0 = 1                    |

| 1-1 = 0                    |

Tabla: Reglas de la Resta Binaria

Solucionar las siguientes Restas Binarias y verificar sus resultados con el sistema numérico decimal:

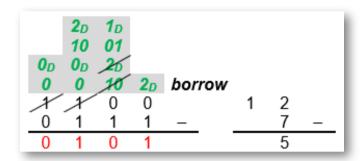

#### ★ Ejemplo 1:

**Paso 1:** se resta del minuendo el sustraendo de C1; como no tiene pide prestado al minuendo de C2:

$$0-1=1$$

$y$   $presta=1$

El minuendo de C2 queda convertido en '0'

Paso 2: se restan los términos de C2:

$$0 - 0 = 0$$

Paso 3: la respuesta de la resta es:

$$10 - 01 = 01_b$$

Paso 4: verificación en el sistema numérico decimal:

$$2 - 1 = 1_d$$

#### ★ Ejemplo 2:

Paso 1: se resta del minuendo el sustraendo de C1; como no tiene pide prestado al minuendo de C2 y el minuendo de C2 no tiene, entonces le pide prestado al minuendo de C3:

$$0 - 1 = 1$$

y  $presta = 1$

Inicialmente, el minuendo de C2 queda convertido en '10', pero al prestarle al minuendo de C1 que queda convertido en '01'

El minuendo de C3 queda convertido en '0'

Paso 2: se resta del minuendo el sustraendo de C2:

$$1 - 1 = 0$$

Paso 3: se resta del minuendo el sustraendo de C3:

$$0 - 0 = 0$$

Paso 4: la respuesta de la resta es:

$$100 - 011 = 001_b$$

Paso 5: verificación en el sistema numérico decimal:

$$4-3=1_d$$

#### ★ Ejemplo 3:

Paso 1: se resta del minuendo el sustraendo de C1; como no tiene pide prestado al minuendo de C2 y el minuendo de C2 no tiene, entonces le pide prestado al minuendo de C3:

$$0 - 1 = 1$$

y  $presta = 1$

Inicialmente, el minuendo de C2 queda convertido en '10', pero al prestarle al minuendo de C1 que queda convertido en '01'

El minuendo de C3 queda convertido en '0'

Paso 2: se resta del minuendo el sustraendo de C2:

$$1 - 1 = 0$$

Paso 3: se resta del minuendo el sustraendo de C3; como no tiene pide prestado al minuendo de C4:

$$10 - 1 = 1$$

Paso 4: se resta del minuendo el sustraendo de C4:

$$0 - 0 = 0$$

Paso 5: la respuesta de la resta es:

$$1100 - 0111 = 0101_b$$

Paso 6: verificación en el sistema numérico decimal:

$$12-7=5_d$$

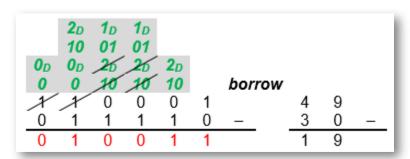

#### ★ Ejemplo 4:

Paso 1: se resta del minuendo el sustraendo de C1; como no tiene pide prestado al minuendo de C2 y el minuendo de C2 no tiene, entonces le pide prestado al minuendo de C3:

$$1 - 1 = 0$$

Paso 2: se resta del minuendo el sustraendo de C2; como no tiene pide prestado al minuendo de C3 y el minuendo de C3 no tiene, entonces le pide prestado al minuendo de C4:

$$10 - 1 = 1$$

y  $presta = 1$

Inicialmente, el minuendo de C3 queda convertido en '10', pero al prestarle al minuendo de C2 que gueda convertido en '01'

El minuendo de C4 queda convertido en '0'

Paso 3: se resta del minuendo el sustraendo de C3:

$$01 - 1 = 0$$

Paso 4: se resta del minuendo el sustraendo de C4; como no tiene pide prestado al minuendo de C5:

$$10 - 1 = 1$$

El minuendo de C5 queda convertido en '0'

Paso 5: se resta del minuendo el sustraendo de C5; como no tiene pide prestado al minuendo de C6:

$$10 - 1 = 1$$

El minuendo de C6 queda convertido en '0'

Paso 6: se resta del minuendo el sustraendo de C6:

$$0 - 0 = 0$$

Paso 7: la respuesta de la resta es:

$$111001 - 011111 = 011010_b$$

Paso 8: verificación en el sistema numérico decimal:

$$57 - 31 = 26_d$$

#### ★ Ejemplo 5:

Paso 1: se resta del minuendo el sustraendo de C1:

$$1 - 0 = 1$$

Paso 2: se resta del minuendo el sustraendo de C2; como no tiene pide prestado al minuendo de C3 y el minuendo de C3 no tiene, entonces le pide prestado al minuendo de C4; como no tiene pide prestado al minuendo de C5:

$$10 - 1 = 1$$

y  $presta = 1$

Inicialmente, el minuendo de C3 queda convertido en '10', pero al prestarle al minuendo de C2 que queda convertido en '01'

Inicialmente, el minuendo de C4 queda convertido en '10', pero al prestarle al minuendo de C3 que queda convertido en '01'

El minuendo de C5 queda convertido en '0'

Paso 3: se resta del minuendo el sustraendo de C3:

$$01 - 1 = 0$$

$y$   $presta = 1$

Paso 4: se resta del minuendo el sustraendo de C4:

$$01 - 1 = 0$$

y  $presta = 1$

Paso 5: se resta del minuendo el sustraendo de C5; como no tiene pide prestado al minuendo de C6:

$$10 - 1 = 1$$

y  $presta = 1$

El minuendo de C6 queda convertido en '0'

Paso 6: se resta del minuendo el sustraendo de C6:

$$0 - 0 = 0$$

Paso 7: la respuesta de la resta es:

$$110001 - 011110 = 010011_b$$

Paso 8: verificación en el sistema numérico decimal:

$$49 - 30 = 19_d$$

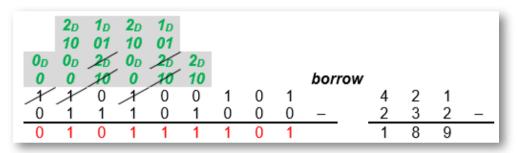

#### ★ Ejemplo 6:

Paso 1: se resta del minuendo el sustraendo de C1:

$$1 - 0 = 1$$

Paso 2: se resta del minuendo el sustraendo de C2:

$$0 - 0 = 0$$

Paso 3: se resta del minuendo el sustraendo de C3:

$$1 - 0 = 1$$

Paso 4: se resta del minuendo el sustraendo de C4; como no tiene pide prestado al minuendo de C5 y el minuendo de C5 no tiene, entonces le pide prestado al minuendo de C6:

$$10 - 1 = 1$$

y  $presta = 1$

Inicialmente, el minuendo de C5 queda convertido en '10', pero al prestarle al minuendo de C4 que queda convertido en '01'

El minuendo de C6 queda convertido en '0'

$$01 - 0 = 1$$

$$10 - 1 = 1$$

y  $presta = 1$

Inicialmente, el minuendo de C7 queda convertido en '10', pero al prestarle al minuendo de C6 que queda convertido en '01'

El minuendo de C8 queda convertido en '0'

$$01 - 1 = 0$$

Paso 8: se resta del minuendo el sustraendo de C8; como no tiene pide prestado al minuendo de C9:

$$10 - 1 = 1$$

El minuendo de C9 queda convertido en '0'

$$0 - 0 = 0$$

$$110100101 - 011101000 = 010111101_b$$

Paso 11: verificación en el sistema numérico decimal:

$$421 - 232 = 189_d$$

Paso 11: verificación en el sistema numérico decimal:

$$421 - 232 = 189_d$$

#### 3.2.1 Otro método de solución

La sustracción o resta es una suma cambiando el signo del sustraendo:

- El signo de un número binario positivo o negativo se cambia hallando su complemento 2.

- Para restar dos números con signo, se calcula el complemento 2 del sustraendo y luego se le suma al minuendo, aplicando las reglas de la suma.

- Los acarreos pueden generar un bit de "desborde" al final de la operación en el extremo izquierdo, este se descarta.

Una forma rápida y fácil de hallar el complemento 2 de un número es:

- Se toma el número de derecha a izquierda (desde el LSB hasta el MSB) y se escriben igual hasta encontrar el primer '1' incluyéndolo.

- 2. A partir del primer '1', se cambian los '1' por '0' y viceversa, hasta llegar al final del número.

- 3. El resultado final es el valor obtenido.

Solucionar las mismas Restas Binarias anteriores utilizando este método y verificar sus resultados:

#### ★ Ejemplo 1:

Paso 1: hallar el complemento 2 del sustraendo de la operación:

- Se escribe igual hasta el primer '1', incluyéndolo = 1

- Se cambian los '1' por '0' y viceversa = 1

- El número completo es = 11

- **Paso 2:** se suma el minuendo de la resta con el número obtenido en complemento 2:

$$10 + 11 = 101$$

se descarta el 1

Paso 3: la respuesta de la operación es:

$$01_b=1_d$$

#### ★ Ejemplo 2:

Paso 1: hallar el complemento 2 del sustraendo de la operación:

- Se escribe igual hasta el primer '1', incluyéndolo = 1

- Se cambian los '1' por '0' y viceversa = 10

- $\circ$  El número completo es = 101

Paso 2: se suma el minuendo de la resta con el número obtenido en complemento 2:

$$100 + 101 = 1001$$

se descarta el 1

Paso 3: la respuesta de la operación es:

$$001_b = 1_d$$

#### ★ Ejemplo 3:

Paso 1: hallar el complemento 2 del sustraendo de la operación:

- Se escribe igual hasta el primer '1', incluyéndolo = 1

- Se cambian los '1' por '0' y viceversa = 100

- El número completo es = 1001

Paso 2: se suma el minuendo de la resta con el número obtenido en complemento 2:

$$1100 + 1001 = 10101$$

se descarta el 1

Paso 3: la respuesta de la operación es:

$$0101_b = 5_d$$

#### ★ Ejemplo 4:

Paso 1: hallar el complemento 2 del sustraendo de la operación:

- Se escribe igual hasta el primer '1', incluyéndolo = 1

- Se cambian los '1' por '0' y viceversa = 10000

- El número completo es = 100001

Paso 2: se suma el minuendo de la resta con el número obtenido en complemento 2:

$$111001 + 100001 = 1011010$$

se descarta el 1

Paso 3: la respuesta de la operación es:

$$011010_b = 26_d$$

#### ★ Ejemplo 5:

Paso 1: hallar el complemento 2 del sustraendo de la operación:

- Se escribe igual hasta el primer '1', incluyéndolo = 10

- Se cambian los '1' por '0' y viceversa = 1000

- El número completo es = 100010

Paso 2: se suma el minuendo de la resta con el número obtenido en complemento 2:

$$110001 + 100010 = 10101$$

se descarta el 1

Paso 3: la respuesta de la operación es:

$$010011_b = 19_d$$

#### ★ Ejemplo 6:

Paso 1: hallar el complemento 2 del sustraendo de la operación:

- Se escribe igual hasta el primer '1', incluyéndolo = 1000

- Se cambian los '1' por '0' y viceversa = 10001

- El número completo es = 100011000

**Paso 2:** se suma el minuendo de la resta con el número obtenido en complemento 2:

$$110100101 + 100011000 = 10101$$

se descarta el 1

Paso 3: la respuesta de la operación es:

$$010111101_b = 189_d$$

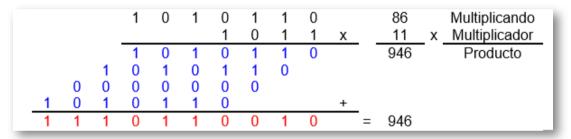

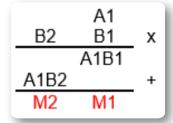

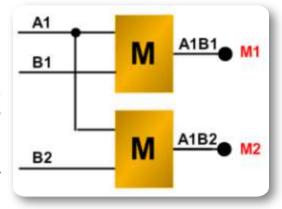

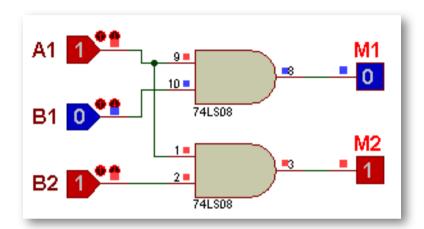

# 3.3 Multiplicación lógica Binaria

La multiplicación de números binarios se realiza de forma similar a la multiplicación de números decimales, salvo que la suma de los productos parciales se realiza en binario.

| Multiplicación Binaria |

|------------------------|

| 0 x 0 = 0              |

| 0 x 1 = 0              |

| 1 x 0 = 0              |

| 1 x 1 = 1              |

**Tabla:** Reglas de la Multiplicación Binaria

Solucionar las siguientes Multiplicaciones Binarias y verificar sus resultados con el sistema numérico decimal:

## ★ Ejemplo 1:

Paso 1: se realiza el producto de cada bit Multiplicador por cada bit del **Multiplicando**:

$$0 \times 11 = 00$$

$$1 \times 11 = 11$$

Paso 2: se suman los anteriores resultados parciales respetando las posiciones que ocupan dentro de la solución del producto:

Paso 3: el resultado de la multiplicación es:

$$11 \times 10 = 110_b = 6_d$$

Paso 4: verificación en el sistema numérico decimal:

$$3 imes2=6_d$$

### ★ Ejemplo 2:

$$1 \times 110 = 110$$

$$1 \times 110 = 110$$

$$1 \times 110 = 110$$

Paso 3: el resultado de la multiplicación es:

$$110 \times 111 = 101010_b = 42_d$$

Paso 4: verificación en el sistema numérico decimal:

$$6 imes 7 = 42_d$$

#### ★ Ejemplo 3:

$$0 \times 1101 = 0000$$

$$1 \times 1101 = 1101$$

$$0 \times 1101 = 0000$$

$$1 \times 1101 = 1101$$

Paso 3: el resultado de la multiplicación es:

$$1101 \times 1010 = 10000010_b = 130_d$$

Paso 4: verificación en el sistema numérico decimal:

$$13 \times 10 = 130_d$$

#### ★ Ejemplo 4:

$$0 \times 10110 = 00000$$

$$1 \times 10110 = 10110$$

$$0 \times 10110 = 00000$$

$$1 \times 10110 = 10110$$

Paso 3: el resultado de la multiplicación es:

$$10110 \times 1010 = 110111100_b = 220_d$$

Paso 4: verificación en el sistema numérico decimal:

$$22 \times 10 = 220_d$$

#### ★ Ejemplo 5:

$$1 \times 1010110 = 1010110$$

$$1 \times 1010110 = 1010110$$

$$0 \times 1010110 = 0000000$$

$$1 \times 1010110 = 1010110$$

Paso 3: el resultado de la multiplicación es:

$$1010110 \times 1011 = 1110110010_b = 946_d$$

Paso 4: verificación en el sistema numérico decimal:

$$86 \times 11 = 946_d$$

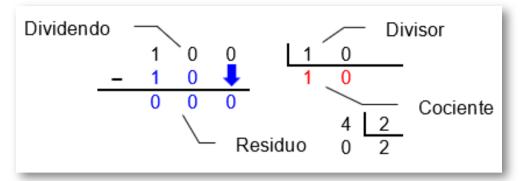

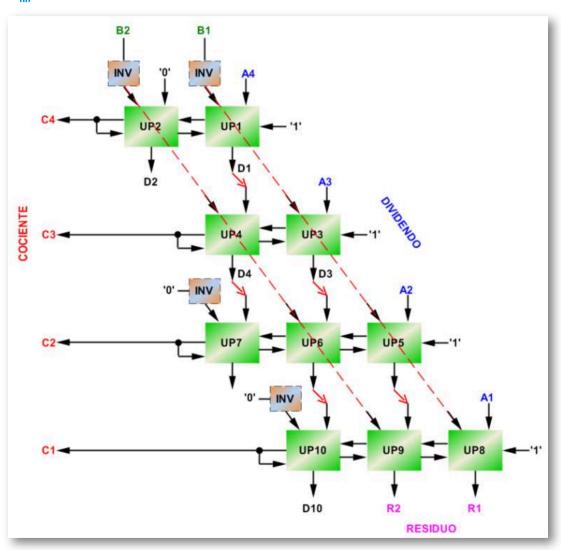

# 3.4 División lógica Binaria

Se realiza de forma similar a la división de los números decimales, salvo que las multiplicaciones y restas internas al proceso de la división se hacen en sistema numérico binario.

| División Binaria |

|------------------|

| 0 ÷ 1 = 0        |

| 1 ÷ 1 = 1        |

Tabla: Reglas de la División Binaria

Solucionar las siguientes Divisiones Binarias y verificar sus resultados con el sistema numérico decimal:

## ★ Ejemplo 1:

- Paso 1: como el Divisor tiene 2 bits (10), se toman igualmente 2 bits en el Dividendo (10):

- $\circ$  El Dividendo > Divisor y lo contiene **1** vez

- $\circ$  Se realiza el producto de:  $1 \times 10 = 10$

- Se halla la diferencia entre: 10 10 = 00

# Paso 2:

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '000'

- $\circ$  Como el nuevo Dividendo < Divisor se coloca un  $oldsymbol{0}$  en el Cociente

- o Como no hay más bits para bajar, la operación termina.

- Paso 3: los resultados del Cociente y el Residuo son:

Cociente:

$$10_b = 2_d$$

Residuo:

$$000_b = 0_d$$

Paso 4: verificación en el sistema numérico decimal:

$$4 \div 2 = 2_d$$

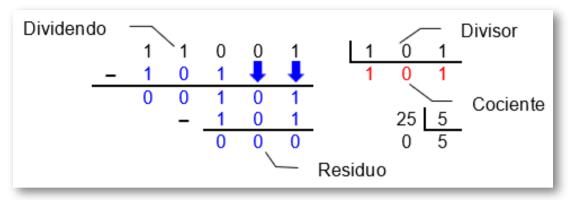

#### ★ Ejemplo 2:

**Paso 1:** como el Divisor tiene 3 bits (101), se toman igualmente 3 bits en el Dividendo (110):

- $\circ$  El Dividendo > Divisor y lo contiene **1** vez

- $\circ$  Se realiza el producto de:  $1 \times 101 = 101$

- Se halla la diferencia entre: 110 101 = 001

#### Paso 2:

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '0010'

- $\circ$  Como el Dividendo < Divisor se coloca un  $oldsymbol{0}$  en el Cociente

- Se baja otro bit (1) y el nuevo Dividendo es '00101'

- $\circ$  Como el Dividendo > Divisor se coloca un  ${f 1}$  en el Cociente

- Se realiza la operación:  $1 \times 101 = 101$

- Se halla la diferencia entre: 101 101 = 000

- Como no hay más bits para bajar, la operación termina

Paso 3: los resultados del Cociente y el Residuo son:

Cociente:

$$101_b = 5_d$$

Residuo:

$$000_b = 0_d$$

Paso 4: verificación en el sistema numérico decimal:

$$25 \div 5 = 5_d$$

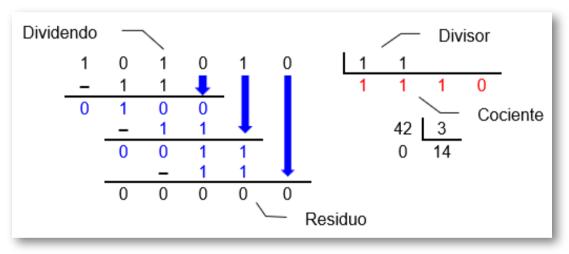

#### ★ Ejemplo 3:

Paso 1: como el Divisor tiene 2 bits (11), se toman igualmente 2 bits en el Dividendo (10):

- $\circ$  Como el Dividendo < Divisor, se toma otro bit del Dividendo (101)

- $\circ$  El Dividendo > Divisor y lo contiene se coloca un 1 en el Cociente

- Se realiza el producto de:  $1 \times 11 = 11$

- Se halla la diferencia entre: 101 11 = 010

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '100'

- Como el nuevo Dividendo > Divisor y lo contiene, se coloca un 1 en el Cociente

- Se realiza el producto de:  $1 \times 11 = 11$

- Se halla la diferencia entre: 100 11 = 001

# **Paso 3:**

- Se baja el bit '1' del Dividendo y el nuevo Dividendo es '011'

- Como el nuevo Dividendo > Divisor y lo contiene, se coloca un 1 en el Cociente

- Se realiza el producto de:  $1 \times 11 = 11$

- Se halla la diferencia entre: 011 011 = 000

# Paso 4:

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '000'

- $\circ$  Como el nuevo Dividendo < Divisor y NO lo contiene, se coloca un  ${f 0}$  en el Cociente

- Como no hay más bits para bajar, la operación termina

Cociente:  $1110_b = 14_d$

$Residuo: 000_b = 0_d$

Paso 6: verificación en el sistema numérico decimal:

$$42 \div 3 = 14_d$$

#### ★ Ejemplo 4:

Paso 1: como el Divisor tiene 3 bits (110), se toman igualmente 3 bits en el Dividendo (110):

- $\circ$  El Dividendo = Divisor y lo contiene se coloca un 1 en el Cociente

- Se realiza el producto de:  $1 \times 110 = 110$

- Se halla la diferencia entre: 110 110 = 000

# Paso 2:

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '000'

- $\circ$  Como el nuevo Dividendo < Divisor y NO lo contiene, se coloca un 0 en el Cociente

# **Paso 3:**

- o Se baja el bit '1' del Dividendo y el nuevo Dividendo es '001'

- $\circ$  Como el nuevo Dividendo < Divisor y NO lo contiene, se coloca un 0 en el Cociente

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '010'

- Como el nuevo Dividendo < Divisor y NO lo contiene, se coloca un 0 en el Cociente

- Como no hay más bits para bajar, la operación termina

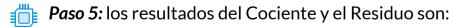

Paso 5: los resultados del Cociente y el Residuo son:

Cociente:  $1000_b = 8_d$

$Residuo: 010_b = 2_d$

Paso 6: verificación en el sistema numérico decimal:

$$50 \div 6 = 8_d y sobra 2_d$$

#### ★ Ejemplo 5:

Paso 1: como el Divisor tiene 4 bits (1000), se toman igualmente 4 bits en el Dividendo (1101):

- $\circ$  El Dividendo > Divisor y lo contiene se coloca un 1 en el Cociente

- $\circ$  Se realiza el producto de:  $1 \times 1000 = 1000$

- Se halla la diferencia entre: 1101 1000 = 0101

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '1010'

- $\circ$  Como el nuevo Dividendo > Divisor y lo contiene, se coloca un 1 en el Cociente

- $\circ$  Se realiza el producto de:  $1 \times 1000 = 1000$

- Se halla la diferencia entre: 1010 1000 = 0010

# Paso 3:

- Se baja el bit '0' del Dividendo y el nuevo Dividendo es '0100'

- $\circ$  Como el nuevo Dividendo < Divisor y NO lo contiene. se coloca un 0 en el Cociente

# Paso 4:

- Se baja el bit '1' del Dividendo y el nuevo Dividendo es '1001'

- $\circ$  Como el nuevo Dividendo > Divisor y lo contiene, se coloca un 1 en el Cociente

- $\circ$  Se realiza el producto de:  $1 \times 1000 = 1000$

- $\circ$  Se halla la diferencia entre: 1001 1000 = 0001

- Se baja el bit '1' del Dividendo y el nuevo Dividendo es '0011'

- Como el nuevo *Dividendo < Divisor* y NO lo contiene. se coloca un 0 en el Cociente

- Como no hay más bits para bajar, la operación termina.

Paso 6: los resultados del Cociente y el Residuo son:

Cociente:

$$11010_b = 26_d$$

Residuo:

$$0011_b = 3_d$$

Paso 7: verificación en el sistema numérico decimal:

$$211 \div 8 = 26_d y \, sobra \, 3_d$$

# 3.5 Ejercicios propuestos con respuesta

Solucionar las siguientes Sumas Binarias y verificar sus resultados con el sistema numérico decimal:

1.

$$100111 + 11011_b \triangleright R/. 1000010_b / 66_d$$

2.

$$111011 + 10101_b \triangleright R/. 1010000_b / 80_d$$

3.

$$10111 + 1011 + 1101_b \triangleright R/. 101111_b / 47_d$$

4.

$$11100 + 1001 + 1100_b \triangleright R/. 100_b / 49_d$$

5.

$$11001 + 10100 + 11101_b \triangleright R. 1001010_b / 74_d$$

Solucionar las siguientes Restas Binarias y verificar sus resultados con el sistema numérico decimal:

- 1.  $10011 1011_b \triangleright R/. 1000_b/8_d$

- 2.  $11010 1110_b \triangleright R/. 1100_b / 12_d$

- 3.  $10000 1111_b \triangleright R/.0001_b / 1_d$

- 4.  $110101110 11101001_b \triangleright R/. 11000101_b / 197_d$

- 5.  $1001111 101010_b \triangleright R/. 100101_b / 37_d$

Solucionar las siguientes Multiplicaciones Binarias y verificar sus resultados con el sistema numérico decimal:

- 1.  $10010 \times 11_b \triangleright R/. 110110_b / 54_d$

- 2.  $1111 \times 101_{h} \triangleright R/. 1001011_{h} / 75_{d}$

- 3.  $11000 \times 110_{h} \triangleright R/. 10010000_{h} / 144_{d}$

- 4.  $11011 \times 100_{h} \triangleright R/. 101101100100_{h} / 135_{d}$

- 5.  $11110 \times 11_{h} \triangleright R/. 1011010_{h}/90_{d}$

Solucionar las siguientes Divisiones Binarias y verificar sus resultados con el sistema numérico decimal ( R/. Cociente y Residuo):

- 1.  $111100 \div 100_{h} \triangleright R/. 1111_{h}/15_{d}$

- 2.  $101100 \div 11_b \triangleright R. 1110 y 10_b / 14 y 2_d$

- 3.  $1001101 \div 1000_b \triangleright R/. 1001 y 101_b / 9 y 5_d$

- 4.  $1101001 \div 1010_b \triangleright R/. 11010 y 101_b / 10 y 5_d$

- 5.  $100110010 \div 1100_b \triangleright R/. 110001 \text{ y } 110_b/25 \text{ y } 6_d$

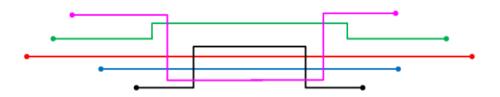

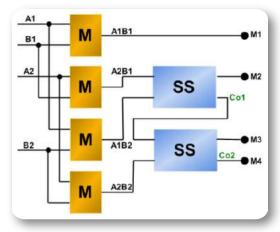

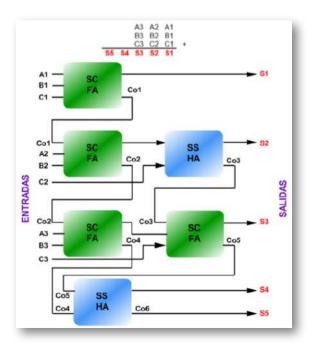

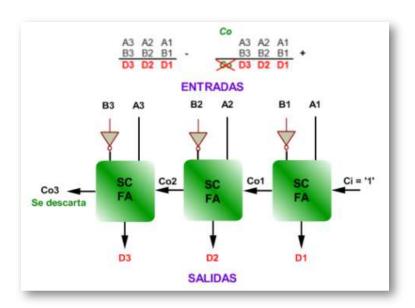

### 3.6 Circuitos Sumadores

Por medio de los circuitos lógicos combinacionales (compuertas lógicas) se pueden implementar circuitos que realicen sumas.

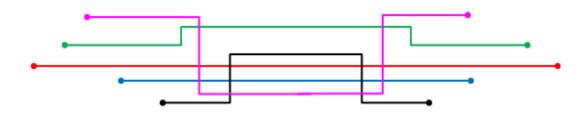

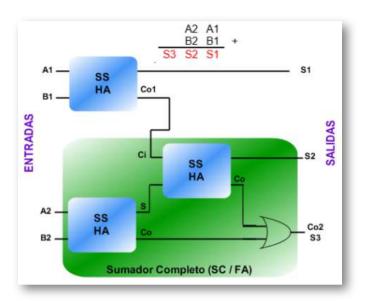

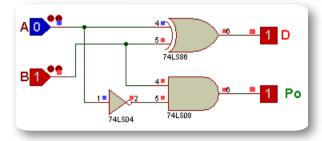

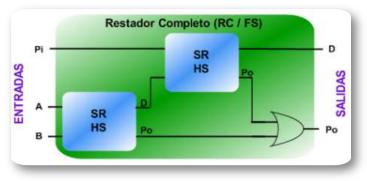

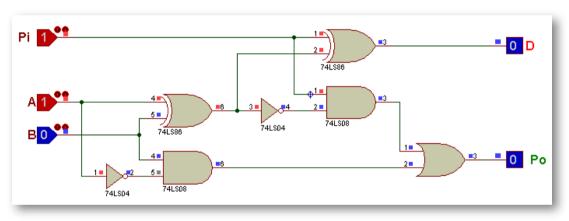

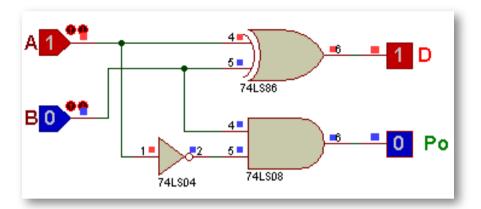

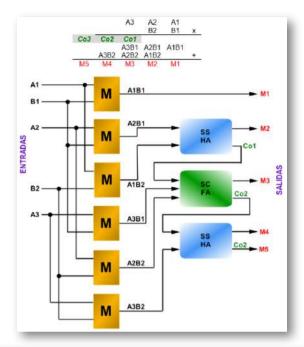

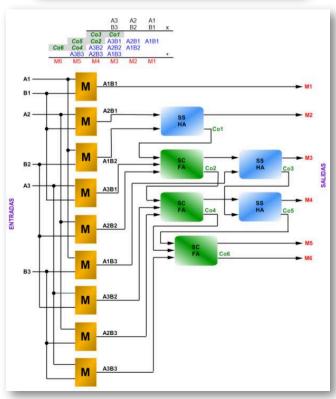

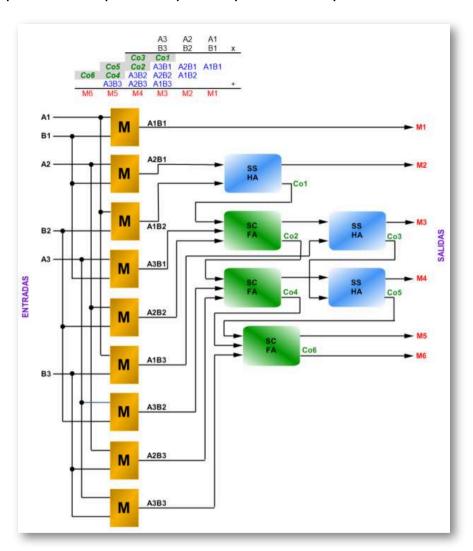

### 3.6.1 Semi-Sumador (SS)

El circuito Semi Sumador (SS = Semi Sumador, HA = Half Adder) se utiliza para sumar dos bits de datos únicamente y su diagrama en bloques es:

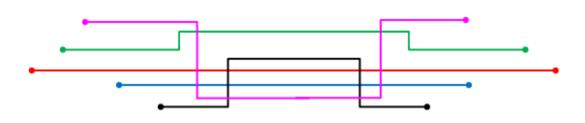

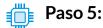

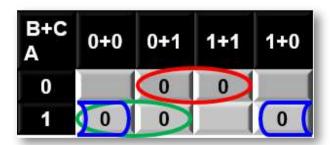

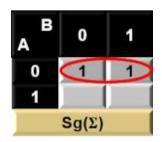

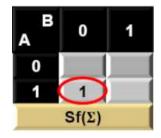

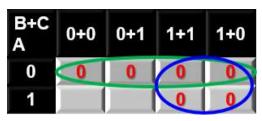

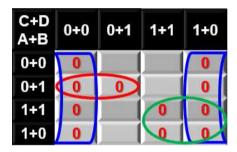

En la tabla de verdad del **Semi Sumador** se observa que la salida ( $\Sigma$ ) cumple con la tabla de verdad de la compuerta lógica **XOR**.

| Sumandos |          | Suma | Acarreo |

|----------|----------|------|---------|

| Α        | В        | Σ    | Со      |

| 0        | 0        | 0    | 0       |

| 0        | 1        | 1    | 0       |

| 1 (      | 0        | 1    | 0       |

| 1 (      | 1        | 0    | 1       |

| $A \in$  | $B \mid$ | Σ    | Co      |

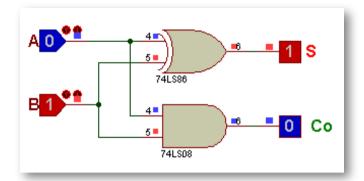

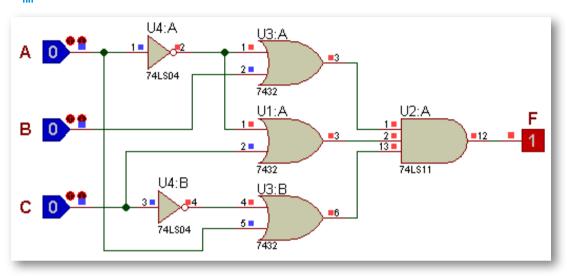

El plano esquemático del circuito semi sumador está compuesto por 2 compuertas lógicas: XOR y AND cada una con dos entradas para los sumandos A y B; y la salida  $\Sigma$  para la Suma y Co para el acarreo (carry).

Las funciones lógicas del Semi Sumador son:

$$S = A \oplus B$$

$$C_o = A \times B$$

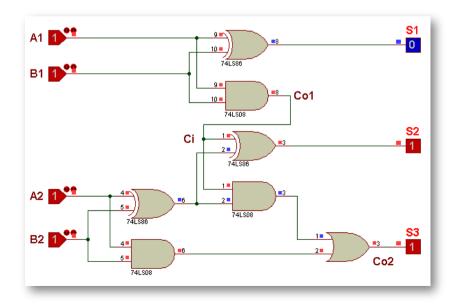

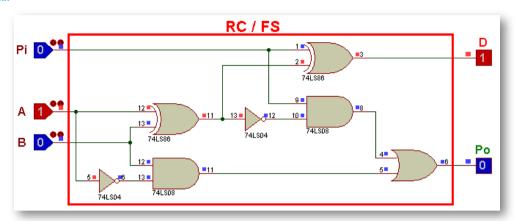

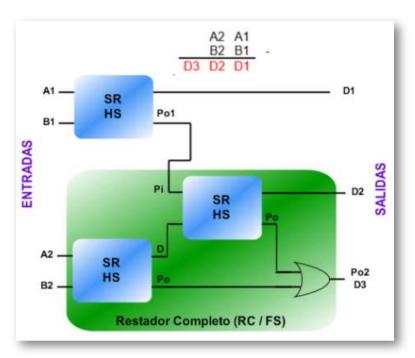

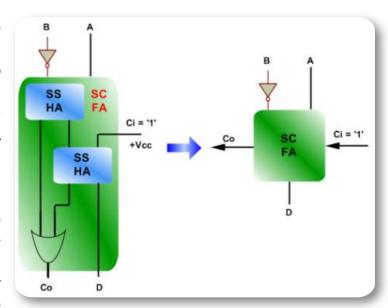

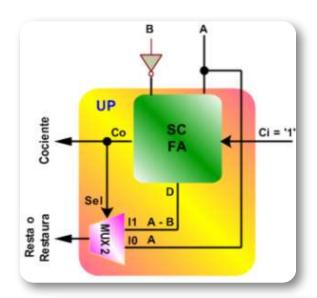

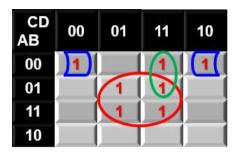

### 3.6.2 Sumador Completo (SC)

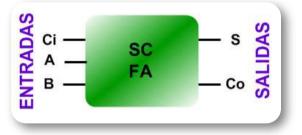

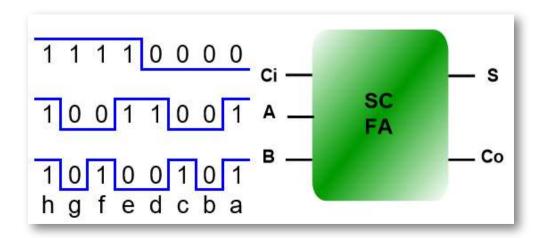

El circuito sumador completo (SC = Sumador Completo, FA = Full Adder) se utiliza para sumar 3 bits de datos y su diagrama en bloques es:

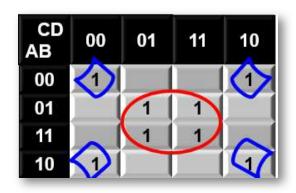

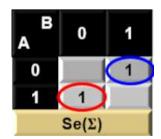

En la tabla de verdad se puede observar el comportamiento del circuito con un *Acarreo de Entrada (Carry In = Ci)* de '0' y de '1'.

|      | <b>Entrad</b> | as                 | Sa   | lidas             |

|------|---------------|--------------------|------|-------------------|

| Suma | andos         | Acarreo<br>Entrada | Suma | Acarreo<br>Salida |

| Α    | В             | Ci                 | Σ    | Со                |

| 0    | 0             | 0                  | 0    | 0                 |

| 0    | 0             | 1 1 (              | 1    | 0                 |

| 0    | 1             | 0 (                | 1    | 0                 |

| 0    | 1             | 1 1                | 0    | 1                 |

| 1    | 0             | 0                  | 1    | 0                 |

| 1    | 0             | 1 1                | 0    | 1                 |

| 1    | 1             | 0                  | 0    | 1                 |

| 1    | 1             | 1 1                | 1    | 1                 |

| A    | 1 + B +       | $C_i$              | Suma | Acarreo           |

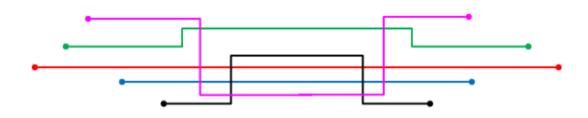

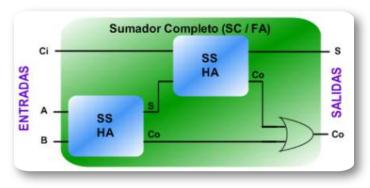

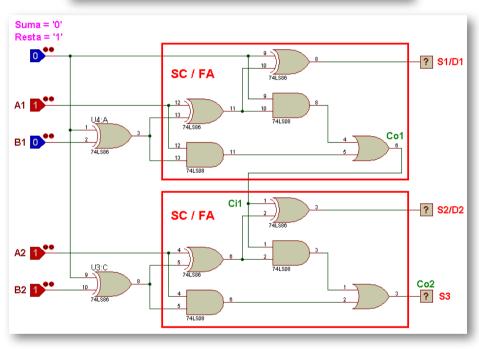

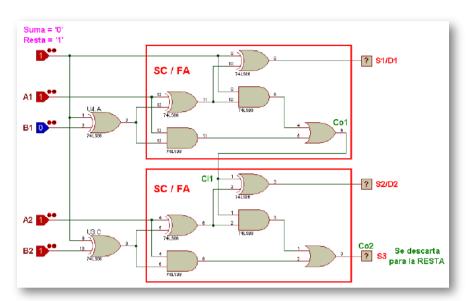

En el diagrama en bloques se observa que el *Sumador Completo (SC)* está conformado por 2 Semi Sumadores (SS) conectados en cascada.

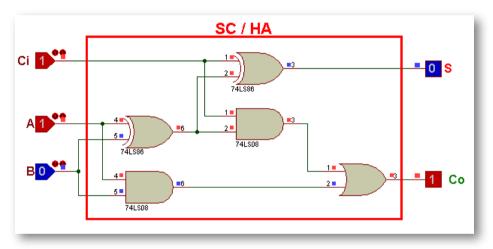

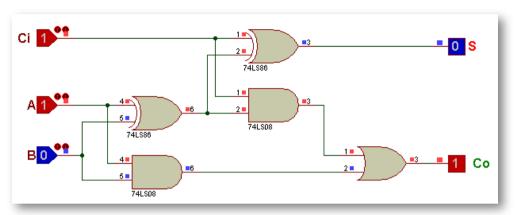

El plano esquemático del Sumador Completo es:

Las funciones lógicas del Sumador Completo son:

$$S = A \oplus B \oplus C_i$$

$C_o = \{C_i imes (A \oplus B)\} + (A imes B)$

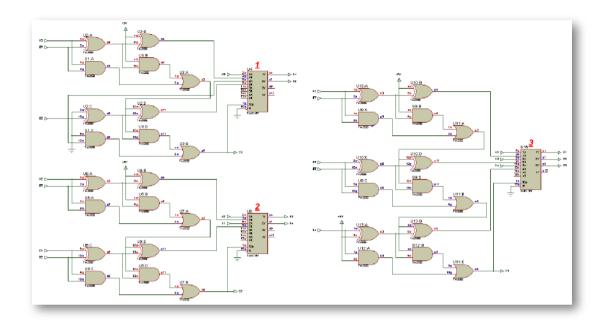

### 3.6.3 Ejemplos

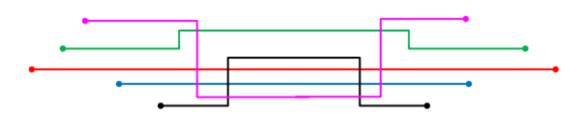

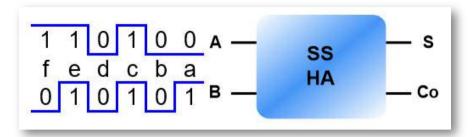

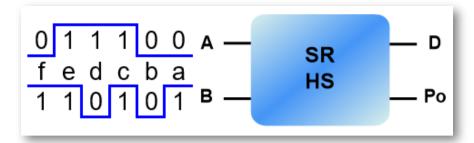

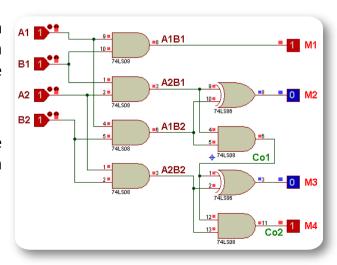

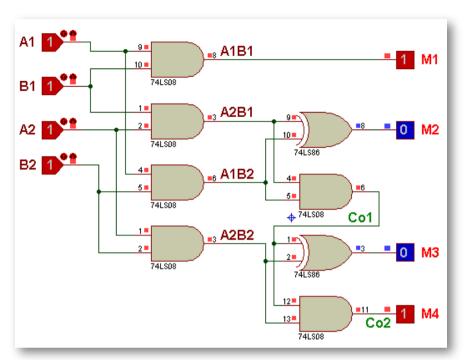

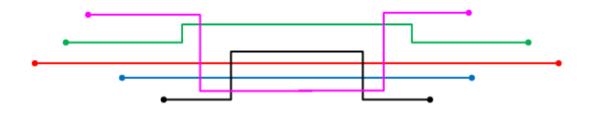

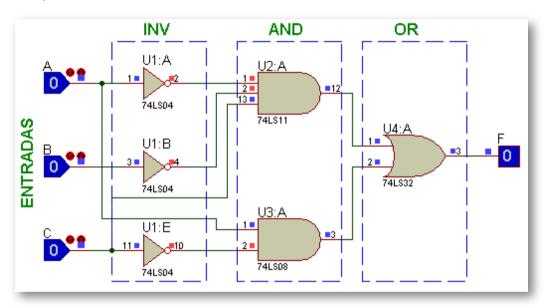

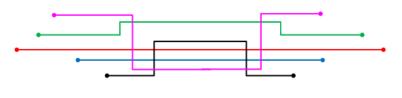

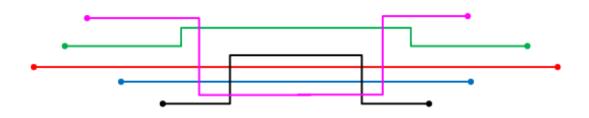

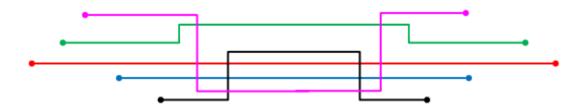

Hallar los estados lógicos en las salidas para cada señal en las entradas del Semi Sumador (SS), tabular toda la información y verificar la solución con un simulador electrónico:

#### **★** Ejemplo 1:

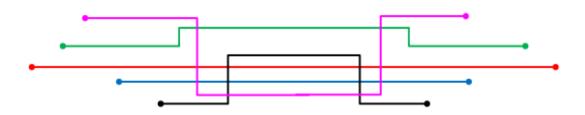

### Paso 1: hallar las salidas para cada pulso de entrada:

- Pulso a: entradas A = '0' y B = '1', las salidas suma = '1' y Co = '0'

- Pulso b: entradas A = '0' y B = '0', las salidas suma = '0' y Co = '0'

- Pulso c: entradas A = '1' y B = '1', las salidas suma = '0' y Co = '1'

- Pulso d: entradas A = '0' y B = '0', las salidas suma = '0' y Co = '0'

- Pulso e: entradas A = '1' y B = '1', las salidas suma = '0' y Co = '1'

- Pulso f: entradas A = '0' y B = '1', las salidas suma = '1' y Co = '0'

### Paso 2: la tabulación de la información es:

Tabla de verdad:

| Entradas |     |     | Sal | idas I |

|----------|-----|-----|-----|--------|

| Pulso    | В   | Α   | Σ   | Co     |

| a        | 1   | 0   | 1   | 0      |

| <b>b</b> | 0   | 0 ( | 0   | 0      |

| C        | 1   | 1 ( | 0   | 1      |

| d        | 0   | 0 ( | 0   | 0      |

| e        | 1 [ | 1 ( | 0   | 1      |

| f        | 0   | 1 ( | 1   | 0      |

### Una imagen de la simulación en Proteus:

Repositorio en <u>Github (Ejemplo-1-SS.dsn)</u> con el archivo de la simulación con Proteus v7.8

#### ★ Ejemplo 2:

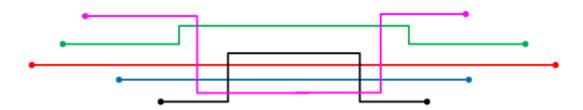

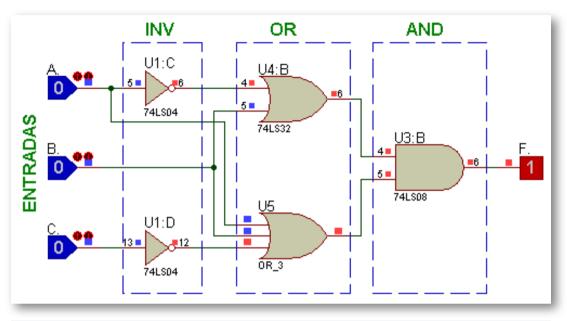

Hallar los estados lógicos en las salidas para cada señal en las entradas del Sumador Completo (SC), tabular toda la información y verificar la solución con un simulador electrónico:

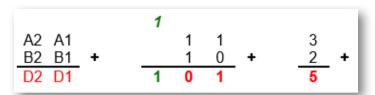

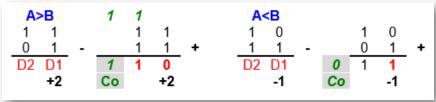

### Paso 1: hallar las salidas para cada pulso de entrada: